### PhD thesis

Michael Kirkedal Carøe

# Design of Reversible Computing Systems

Logic, Languages, and Circuits

Academic advisor: Robert Glück Submitted: July 7, 2012

## Design of Reversible Computing Systems

Logic, Languages, and Circuits

### Michael Kirkedal Carøe

DIKU, Department of Computer Science, University of Copenhagen, Denmark

July 7, 2012

### PhD Thesis

This thesis has been submitted to the PhD School of Science, Faculty of Science, University of Copenhagen, Denmark

| Author:           | Michael Kirkedal Carøe                                                     |

|-------------------|----------------------------------------------------------------------------|

| Born / pen name:  | Michael Kirkedal Thomsen                                                   |

| Affiliation:      | DIKU, Department of Computer Science,<br>University of Copenhagen, Denmark |

| Title:            | Design of Reversible Computing Systems / Logic, Languages, and Circuits    |

| Academic advisor: | Robert Glück                                                               |

| Submitted:        | July 7, 2012                                                               |

#### Short abstract

This thesis investigates garbage-free reversible computing systems from abstract design to physical gate-level implementation. Designed in reversible logic, we propose a ripple-block carry adder and work towards a reversible circuit for general multiplication. At a higher-level, abstract designs are proposed for reversible systems, such as a small von Neumann architecture that can execute programs written in a simple reversible two-address instruction set, a novel reversible arithmetic logic unit, and a linear cosine transform. To aid the design of reversible logic circuits we have designed two reversible functional hardware description languages: a linear-typed higher-level language and a gate-level point-free combinator language. We suggest a garbage-free design flow, where circuits are described in the higher-level language and then translated to the combinator language, from which methods to place-and-route of CMOS gates can be applied. We have also made standard cell layouts of the reversible gates in complementary pass-gate CMOS logic and used these to fabricate the ALU design.

In total, this thesis has shown that it is possible to design nontrivial reversible computing systems without garbage and that support from languages (computer aided design) can make this process easier. For Maja and Augusta

#### Abstract

Reversible computing spans computational models that are both forward and backward deterministic. These models have applications in program inversion and bidirectional computing, and are also interesting as a study of theoretical properties. The motivation for reversible computing comes, however, often from the fact that these models are information preserving. Landauer's principle links information theory and thermodynamics; all information has some physical representation, so a loss of information must cause a thermodynamical entropy decrease, which then leads to heat dissipation to obey the law thermodynamics. A reversible computation does, thus, not have to use energy, though this is impossible to avoid in practice, due to the way computers are build.

It is, however, not always obvious how to implement reversible computing systems. The restriction to avoid information loss, imposes new design criteria that need to be incorporated into the design; criteria that do not follow directly from conventional models. The result is that, today, many implementations is simple reversible embeddings of conventional solutions. This is not a desirable approach, because these simple embeddings always generate garbage, which then leads to erasure of information.

In this thesis I investigate garbage-free reversible computing systems from abstract design to physical gate-level implementation. Arithmetic operations are a basis for many computing systems, so a proposed the design of a ripple-block carry adder and work towards a reversible circuit for general multiplication are important new circuits. Such arithmetic circuits have then been used in the design of two larger reversible computing systems. The first is a small von Neumann architecture, called Bob, that can execute programs written in a simple reversible two-address instruction set. A central part of the architecture is a novel design of a reversible arithmetic logic unit. The second system is an implementation of the linear cosine transform used in the H.264/ACV encoding standard.

Designing reversible logic circuits on paper can become very complex, so I have designed two reversible functional hardware description languages that can simplify the implementation process. One language is a linear-typed higher-level language, while the other is a gate-level point-free combinator language. These two languages can be used in a garbage-free design flow, where circuits are described in the higherlevel language and then translated to the combinator language. From the gate-level language, methods of place-and-route of CMOS gates can be applied. To facilitate this last step, I have also made standard cell layouts of the reversible gates in complementary pass-gate CMOS logic and, as a test, these cells have been used to fabricate the ALU design.

In total, this thesis has shown that it is possible to design non-trivial reversible computing systems without garbage and that support from languages (computer aided design) can make this process easier. However, there is often still a need to rethink both the problem and the solution to accommodate the no-garbage approach.

#### Dansk Resumé

Reversible beregninger dækker over beregningsmodeller der er både forlæns og baglæns deterministiske. Disse modeller finder anvendelse indenfor program inversion og bidirektionel beregning, men er også interessante som et studie af deres teoretiske egenskaber. Motivationen bag reversible beregning kommer dog ofte fra det faktum at disse modeller er informationsbevarende. Landauers princip kæder informationsteori sammen med termodynamikken; al informations har en fysisk repræsentation, så tab af information må medføre en reduktion af termodynamisk entropi, som dermed fører til varmeafgivelse for at overholde termodynamikkens love. En reversibel beregning vil dermed ikke have et varmetab, dog er det i praksis umuligt at undgå pga. datamatens opbygning.

Det er dog ikke altid oplagt hvordan man kan implementere reversible beregningssystemer. Restriktionen om at undgå informationstab, opstiller nye designkriterier, som er nødvendigt at inddrage i designet – kriterier som ikke følger direkte fra konventionelle beregningsmodeller. Resultatet er at mange implementationer i dag er simple reversible indlejringer af konventionelle løsninger. Dette er ikke en ønskelig fremgangsmåde, da disse simple indlejringer altid vil generere "affald", som efterfølgende medfører informationstab.

I denne afhandling undersøges affaldsfrie reversible beregningssystemer fra abstrakt design ned til implementation på fysisk port-niveau. Aritmetiske operationer er grundlaget for mange beregningssystemer, så der foreslås et design til et "ripple-block carry" additionskredsløb og foreløbigt arbejde mod et reversibelt kredsløb for general multiplikation er vigtige nye kredsløb. Sådanne aritmetiske kredsløb er brugt i designet af to større reversible beregningssystemer. Det første er en lille von Neumann arkitektur, kaldet Bob (eng. for lod), som kan udføre programmer skrevet i et simpelt reversibelt to-adresse instruktionssæt. En central del af arkitekturen er et nyt design af en reversibel aritmetisk logisk enhed (ALU). Det andet system er en implementation af en lineær cosinus transformation, som bruges i H.264/AVC videokodningsstandarden.

Design af reversibel logik på papir kan nemt blive meget komplekst, så jeg har udviklet to reversible funktionelle hardwarebeskrivelsessprog, som kan simplificere implementationsforløbet. Det ene er et lineærttypet høj-niveau sprog, mens det andet et 'logisk port'-niveau punkt-frit kombinatorsprog. Fra port-niveau sproget kan så benyttes metoder til placering-og-rutning af CMOS porte. For at facilitere det sidste skridt, har vi også lavet standard celle layout af de reversible porte i komplementær passér-port CMOS logik, og, som en test, har disse celler været brugt til at fabrikere ALU designet.

Alt i alt har denne afhandling vist at det er muligt at designe ikketrivielle reversible beregningssystemer uden affald, og at hjælp fra programmeringssprog (datamat støttet design) kan gøre dette forløb nemmere. Der er dog stadig ofte et behov for at gentænke både problemet og løsningen for at akkommodere *intet-affald fremgangsmåden*.

## Contents

| Preface                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction1.1Information and the Limit of Computation1.2Foundations of Reversible Computing1.3Reversible Logic and Quantum Computing1.4Reversible Programming Languages and Transformation1.5Towards Reversible Computer Organization and Design | $\begin{array}{c} 2\\ 3\\ 4\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Design of Reversible Computing Systems                                                                                                                                                                                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.3 Multimedia Transformation                                                                                                                                                                                                                      | . 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Computer Aided Design of Reversible Circuits                                                                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.1 Reversible Logic Synthesis and Optimization                                                                                                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2 Hardware Description Languages                                                                                                                                                                                                                 | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Realization of Reversible Circuits                                                                                                                                                                                                                 | <b>14</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.1 Adiabatic Switching and Charge Recovery                                                                                                                                                                                                        | . 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2 Embedding in Static CMOS                                                                                                                                                                                                                       | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conclusions and Perspectives                                                                                                                                                                                                                       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.1 Future Work                                                                                                                                                                                                                                    | . 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bibliography                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Papers on Gate-Level Designs of Arithmetic Functions                                                                                                                                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A1 Optimized Reversible Binary-Coded Decimal Adders                                                                                                                                                                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A2 Parallelization of Reversible Ripple-Carry Adders                                                                                                                                                                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A3 Garbage-Free Integer Multiplication with Constants                                                                                                                                                                                              | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Papers on Reversible Architectures                                                                                                                                                                                                                 | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B1 Reversible Arithmetic Logic Unit for Quantum Arithmetic                                                                                                                                                                                         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| B2 A Reversible Processor Architecture and its Reversible Logic<br>Design                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ;;                                                                                                                                                                                                                                                 | Introduction         1.1       Information and the Limit of Computation         1.2       Foundations of Reversible Computing         1.3       Reversible Logic and Quantum Computing         1.4       Reversible Programming Languages and Transformation         1.5       Towards Reversible Computer Organization and Design         1.5       Towards Reversible Computing Systems         2.1       Arithmetic Logic Circuits         2.2       Computing Architectures and Instruction Sets         2.3       Multimedia Transformation         2.4       Reversible Logic Synthesis and Optimization         3.2       Hardware Description Languages         3.4       Reversible Circuits         3.1       Reversible Logic Synthesis and Optimization         3.2       Hardware Description Languages         4.1       Adiabatic Switching and Charge Recovery         4.2       Embedding in Static CMOS         4.3       Embedding in Static CMOS         5.1       Future Work         5.1       Future Work         5.1       Future Work         5.2       Parallelization of Reversible Binary-Coded Decimal Adders         5.3       Garbage-Free Integer Multiplication with Constants         5.4       Parallelization of Rever |

| $\mathbf{C}$ | C Papers on Implementation of Reversible Linear Transforms |                                                                  |     |

|--------------|------------------------------------------------------------|------------------------------------------------------------------|-----|

|              | C1                                                         | Reversible Implementation of a Discrete Integer Linear Trans-    |     |

|              |                                                            | form                                                             | 99  |

|              | C2                                                         | Garbageless Reversible Implementation of Integer Linear Trans-   |     |

|              |                                                            | formations                                                       | 111 |

| D            | Рар                                                        | ers on Design Languages for Reversible Logic                     | 123 |

|              | D1                                                         | Describing and Optimising Reversible Logic using a Functional    |     |

|              |                                                            | Language                                                         | 125 |

|              | D2                                                         | A Functional Language for Describing Reversible Logic            |     |

| $\mathbf{E}$ | E Papers on Engineering of Reversible Circuits 14          |                                                                  | 149 |

|              | E1                                                         | Design of Reversible Logic Circuits using Standard Cells / Stan- |     |

|              |                                                            | dard Cells and Functional Programming                            | 151 |

|              | E2                                                         | Interfacing Reversible Pass-Transistor CMOS Chips with Con-      |     |

|              |                                                            | ventional Restoring CMOS Circuits                                | 179 |

### Preface

This thesis has been submitted to the PhD School of Science, Faculty of Science, University of Copenhagen in partial fulfillment of the requirements for a PhD degree at DIKU, Department of Computer Science, University of Copenhagen, Denmark.

The thesis is written as a synopsis with 11 annexed research papers. The first chapter of the synopsis contains a short introduction to reversible computation and a description of the topic and objectives of the thesis. Following this, are three chapters that detail the contributions of my research and its relation to existing knowledge. The synopsis ends with conclusions and perspectives for future research. References to related work are given throughout the synopsis. Five appendices contains the 11 research papers; of these there are (at the time of writing) 6 published journal and conference papers, 2 pre-print conference papers (accepted for publication), 2 workshop papers, and 1 technical report.

This thesis is not the result of one person's lone fight against the world and it's reckless handling of information. Therefore, I would like to thank my advisor Robert Glück, who introduced me to the subject, and my co-author, office mate, and friend Holger Bock Axelsen. I also thank my other co-authors (the Flemish connection) Alexis De Vos, Stéphane Burignat, Kenneth Vermeirsh, Michał Klimczak, and Mariusz Olczak. The collaboration with Oticon A/S has been important to the direction of the research and, from there, I would especially like to thank Kenneth Branth and Kim Poulsen. Many other people have had an influence on this thesis, so in arbitrary (alphabetic) order I would like thank Jesper Louis Andersen, Patrick Bahr, Poul Johannis Clementsen, Fritz Henglein, Mathias Horn, Susan Nasirumbi Ipsen, Mathias Lehnfeld, Lars Valdemar Mogensen, Torben Æ. Mogensen, Kenji Moriyama, Jette Giovanni Møller, Thomas Pécseli, Claus Rørbech, Mary Sheeran, Jens Sparsø, Christen Artagnan Sørensen, Robert Wille, Tetsuo Yokoyama, and rest of APL group at DIKU. Also, I would like to thank the Danish Strategy Research Council for funding the MicroPower research project and, thus, my PhD stipend.

Finally, I thank my family and friends for their support during this period. Without this, I would not have been able to do all the work and travel.

> Michael Kirkedal Carøe (née Thomsen)

### Introduction

# 1

*Reversible computing* was introduced by Bennett [17] and concerns (universal) computation models where a result can not only be computed, but also uncomputed. We also define these as models that are both forward and backward deterministic. Though reversible computation models can compute all *injective computable functions*, injectivity is not enough to characterize a reversible computing model; we must also require that each computation step is bijective.

This important requirement provides the connection to preservation of information, which is a key motivation for research in reversible computing. A motivation that has its foundation in 1961 with a principle defined by Landauer [79]; a principle that was experimentally verified very recently [20].

#### **1.1** Information and the Limit of Computation

The search to understand the computation process and its limitations is older that computers themselves. Here, we do not think of the algorithmic bounds (which is a very interesting topic by itself), but the limitations that are imposed by the physical world. All computers are situated in the physical world, so the laws of physics, thus, also apply for computers including their circuits and memory. The question is what impact do the laws of physics have on the computation process?

During the 1950's (only shortly after the invention of the modern electronic digital computer [28]) the assumption arose that a logic operation requires an energy dissipation of  $kT \ln 2$ , where k is Boltzmann's constant and T is the temperature at which the operation is performed<sup>1</sup>. Von Neumann has later been credited for saying that this amount of energy is dissipated by two different sources: namely "per elementary decision of a two-way alternative and per elementary transmittal of one unit of information" [153]<sup>2</sup>. From the first source, it *is* apparent that von Neumann meant something less than all computations and it sounds a lot like a conditional, which we today know to be a problem. Today, we also know that the second source does not necessitate energy dissipation (*cf.* [80]).

The breakthrough came in 1961 when Landauer [79] argued that all logical operations are associated with a physical operation and because physical irreversibility requires heat generation, then so does logical irreversibility. It is,

<sup>&</sup>lt;sup>1</sup>This assumption followed from earlier work by Szilard [136] and Shannon [125] that argued that communicating one bit required this dissipation (cf. [81]).

$<sup>^{2}</sup>$ John von Neumann died in 1957; four years before Landauer's seminal paper. The paper was finished by Burks and published in 1966, but the work still dates back to the 1950's.

thus, not the computation process itself that necessitates energy dissipation, but the process of deleting information. Today, we refer to this as *Landauer's principle*, and the dissipation of  $kT \ln 2$  Joules per deleted bit of information is called *Landauer's* limit<sup>3</sup>. Landauer founded his principle on a thought experiment in which each bit of information is encoded in a single particle. This is extremely hard to implement in the physical world, nonetheless, Landauer's principle was experimentally verified very recently [20].

At the time of Landauer's paper (and in the following decade) it was, however, believed that erasing information was an unavoidable consequence of a computation process. Landauer had realized that all irreversible operations can be embedded in a reversible operation and, as an example, he embedded the AND gate in the reversible gate that we today call a *Toffoli gate*. He, however, only imagined that these *Landauer embeddings* could be used to temporally store the inputs of each gate, which then had to be deleted later, thus, leading to irreversibility.

#### **1.2** Foundations of Reversible Computing

The second breakthrough came in 1973 with Bennett's seminal paper [17], where he defined the first universal reversible computation model; he constrained the conventional (irreversible) Turing machines (TMs) to define the reversible Turing machines (RTMs)<sup>4</sup>. In this paper Bennett also demonstrates how to embed an irreversible TM in an RTM using a history tape (similar to Landauer's embedding) and then run this RTM with a compute-copyuncompute method (today we call this *Bennett's method*) such that the overall result is only the input and the calculated output. This is a significant improvement over the use of a general trace, but often we are only interested in the result of a calculation and not both the input and output. Bennett later showed [18] how, for injective functions, this input can be uncomputed by using more time, viz. adding an extra compute-copy-uncompute phase. This is a very important result. In our research, we seek here to completely avoid garbage, because we need to know what is possible within the computational models. If needed, for a practical implementation perspective, it is easier to relax this criteria than it is strengthen it. Further research in the tradeoff between time and space on one hand, and erasure of information (garbage) on the other have been performed by Bennett, Levine, Sherman, Vitanyi, and more [19, 30, 86, 152, 162].

After Bennett's seminal paper, focus in reversible computation was directed towards more practical models (see Sections 1.3 and 1.4). But at the beginning of the 1990's, interest in the theoretical aspects increased [18, 67, 86, 119] and since then *computability and complexity* of the reversible model has developed into a research area by itself; trying to find the place within the *Complexity Zoo* [1] for the reversible complexity classes. This has lead to research both on RTMs [7, 10, 11, 25, 35, 83] and different models of *reversible automata* [9, 77, 107–110]. An interesting result being that reversible space equals deterministic space [83].

$<sup>^{3}</sup>$ In practice the dissipation per bit is proportional to the signal energy used to represent the bit [58] and the actual dissipation is, thus, expected to be higher.

<sup>&</sup>lt;sup>4</sup>The first mention of reversible Turing machines can be dated back to Lecerf in 1963 [84].

#### **1.3** Reversible Logic and Quantum Computing

From the beginning, logic has had a central place in the ideas of reversible computing; *e.g.* Landauer's ideas for the reversible gates were designed as a method to reduce the heat dissipation of logic circuits.

Inspired by Landauer's and Bennett's work, Fredkin and Toffoli had, in 1978, been working to design a reversible computer that should be based on conservative logic  $[55]^5$ . In conservative logic all logic gates must be both reversible and parity preserving; *i.e.* the number of TRUE values must also be preserved over the gate. For this they introduced the *Fredkin gate*, which can be characterized as a controlled-swap  $gate^{6}$ . The model was developed to reflect fundamental physical principles and they developed a billiard ball model with a physical representation of the Fredkin gate. Conservative logic is, however, a stricter model than reversible logic, so in 1980 Toffoli presented the n-bit controlled-not gates [144]. This is the most widely used class of reversible gates today, because the gates have a simple mathematical definition, which makes reversible logic synthesis easier (see Section 3). The class covers the not, Feynman, and Toffoli gates. To follow the idea of the Fredkin gate, Toffoli also presented ingenious physical designs of these gates [145] based on 'differential gears' to implement the XOR and a 'rotating cam' to implement the AND in the Toffoli gate.

At the same time as Fredkin and Toffoli's work, other people were developing ideas for another radically new computer design. In 1980 Benioff presented his paper on how to design a (classical) computer from quantum components [16], which shortly after (in 1982) was followed by Feynman's paper on a computer that can simulate quantum physics [47]. In 1985 Deutsch presented his *universal quantum computer* [44] and the new field was born.

In the quantum model, it was easy to include Fredkin and Toffoli's gates and in 1985 Feynman, with his flair for intuitive graphical descriptions, introduced the diagram notation that is used today [48]. In this paper, Feynman also introduced the very first reversible arithmetic circuits; these circuits include a full-adder implementation with four reversible gates. More (reversible) quantum gates (e.g. [116]) and different notation were introduced, so in 1995 Barenco, Bennett, Shor, and others worked as a 'standardization committee' and decided on the notation and a set of universal quantum gates [15].

From a historical perspective, the idea of reversible logic circuits are even older than Fredkin and Toffoli's work. In 1959, two years before Landauer's paper, Huffman looked at *information-lossless* finite state machines (FSMs) [66]. He was interested in signal transformation (both for encoding and cryptography) and for these applications information-lossless FSMs are perfect; by constructing the encoding machine you also get the decoding machine. To design these FSMs, he defined information-lossless gates similar to reversible gates. Huffman also showed that adding a control signal calculated by an irreversible function to a reversible gate, does not break reversibility of the gate. The circuits are, however, not reversible according to our definition, but this was also not his purpose.

$<sup>^5 {\</sup>rm Fredkin}$  and Toffoli's paper was published in 1982, but the paper was based on internal papers and an MIT course from 1978; see [144, References]

$<sup>^{6}</sup>$ The gate that Fredkin and Toffoli presented swapped the two input-values if the control is FALSE. The Fredkin gate that we use today swaps if the control is TRUE.

#### 1.4 Reversible Programming Languages and Transformation

Another track in the history of reversible computing begins in 1986. At this time, Lutz, after a brief meeting with Landauer, sent him a letter about some work he did with Derby, about four years earlier, on a reversible imperative language called Janus [90]. Their work arose from an interest to investigate if it was possible to implement such a language and before 1986 Lutz and Derby did not know about Landauer's principle. The language was 'rediscovered' after the turn of the century and has since then been formalized and further developed at DIKU [32, 161, 164]; here, also student projects that implement more advanced algorithms (*e.g.* matrix multiplication) have been made [70,91]. Other simple reversible imperative languages have been developed, *e.g.* Frank developed R [52] generate instruction code for the Pendulum processor and Matos [96] made a language for linear programs.

Though the first reversible programming language was imperative, reversible functional languages have lately received the most interest. This development started in 1996 when Huelsbergen presented SECD-H [65], an evaluator for the lambda calculus that extended Landin's SECD evaluator [82] with a history tape. (Kluge [73] similarly extended a machine that can reduce a program term to normal-form and back again.) This was followed by Mu *et al.* who, with applications in bidirectional computing in mind, presented a reversible relational language [111]. More recently, work towards general purpose functional programming languages was presented independently by Yokoyama, Axelsen, Glück [163] and James, Sabry [68].

Also, a variety of languages for modeling quantum computations have been designed in almost all different paradigms. We will not detail these here, but refer to Gay's survey of the area [57].

On a related topic, transformation of reversible languages have also received some interest lately (mainly at DIKU). Though the first compiler between two reversible language was made by Frank [52] (between his language R and a reversible instruction set called PISA), it was Axelsen who devised techniques for a compiler that could perform clean translation [8]. His translation was between Janus and PISA and was clean in the sense that the compiled program did not have more than a constant memory overhead over the original Janus program. It is likely that the PISA program will use more temporary memory/registers. Mogensen's also did work on partial evaluation of Janus [105, 106].

We would also like to mention (automatic) program inversion. Inverting a reversible program is often easy, but if the program is implemented in a irreversible language it is harder. Program inversion has a direct impact on program maintainability and reliability of the inverse programs, which are otherwise hard to find if the program to be inverted either is formulated in a conventional programming language [97,133], or have to be deduced by static program analysis techniques [59] or interpretation [2]. We should also mention semi-inversion, where the inverted program not necessarily is a mapping from output to input, but a combination of the original inputs and outputs, cf. Mogensen [103, 104].

Work on reversible instruction sets is covered in Section 2, while design language for reversible logic is discussed in Section 3.2.

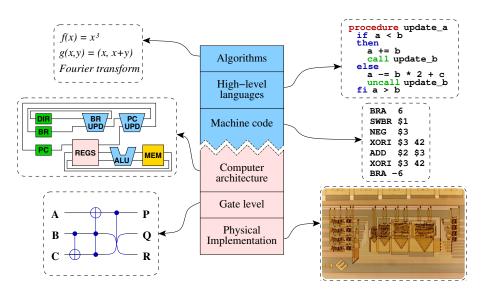

Figure 1.1: Tower of reversible computing system [12].

#### 1.5 Towards Reversible Computer Organization and Design

In his 1961 paper, Landauer wrote that "we shall label a machine as being logical reversible, if and only if all its individual steps are logically reversible" [79]. This is a very grand challenge and we know from Bennett (and later work) that, theoretically, such machines *do* exist – even when we add the requirement that the final result must not include garbage. But is it possible to realize such machines in practice and can it be done with the fabrication technology that exists today? And will we actually be able to achieve the expected reduced heat dissipation?

The *MicroPower* research project [12], which started in 2009, has as objective to develop a *proof-of-concept reversible computing system* and the computer science theory behind it. To do this all parts of the *reversible computation tower* (Figure 1.1) must be investigated. More specifically, the project investigates whether reversible computing can be applied in a power-limited application (specifically hearing aids) with the future hope to either reduce power consumption or increase functionality.

This dissertation is part of the MicroPower research project. Within this project, my thesis is that making a garbage-free reversible computing system is not only feasible, but does not necessarily require much more effort than making a conventional computing system. We will *not* address the questions of the actual energy consumption of the circuits and the theoretical implications; these two fundamental questions are investigated by other parts of the project.

To answer our thesis we must investigate the bottom part of the computing tower (Figure 1.1) from the machine code level down to the physical implementation. We investigate and design basic reversible logic circuits with an emphasis on arithmetic (Section 2.1). These are important basic operations in all computing systems and will, therefore, give the foundation for the reversible systems. Improvements here will improve all other parts of the tower. We also look at reversible circuits from a higher abstraction, namely in terms of logic designs of reversible computer architectures (Section 2.2) and multimedia transforms (Section 2.3). These two applications have the potential to be the first practical use of reversible circuits: architectures to create very small stand-alone systems (*e.g.* sensors) and multimedia transforms, which can be embedded in an irreversible system.

We investigate different *computer aided design* (CAD) approaches for reversible circuits (Section 3). Logic circuits designed by hand are often efficient, but it is very time consuming and verification of the designs are not practical. The purpose of a hardware description language is to raise this abstraction. Finally, we investigate how to implement reversible circuits in CMOS (Section 4). Here we desire implementations that can be used with the CAD process, but still have the prospect of reduced energy consumption. We will also look into how reversible CMOS circuits can be embedded in 'conventional' static CMOS circuits. Finally, we will look at future research topics (Section 5).

### Design of Reversible Computing Systems

# 2

To avoid the heat dissipation from Landauer's principle the entire computing system must be fully reversible. In this chapter we will look at designs of reversible computing systems at and close to the logic gate level. We first focus on design of arithmetic logic circuits. Then, based on these, we look at reversible computing architectures and designs of multimedia transforms.

#### 2.1 Arithmetic Logic Circuits

Arithmetic operations lie at the foundation of most computing systems and good logical implementations of these are important. Improvements to arithmetic circuits can result in improvements to the entire computing system. In a garbage-free reversible computing system it is especially important that the arithmetic circuits are also garbage-free, but how to do this is not always obvious, and history shows that rethinking our current knowledge can be necessary.

#### Addition

An immediate problem for reversible adder implementation is that addition is *not* an injective function in itself: given just the value of the sum A + B, one can not determine A and B uniquely. We can, however, redefine the problem by using *reversible updates* [13] and to avoid overflow we use *n*-bit modular addition,  $(A, B) \mapsto (A, B + A \mod 2^n)$ , to define reversible addition.

The adder that Feynman proposed [48] was a reversible *embedding* of the ripple-carry adder. Though addition is an injective function if one of the inputs is kept, the conventional ripple-carry structure is *not* reversible. The problem lies in the use of the full-adder circuit, because it is not possible to calculate both the sum and the carry without copying one of the inputs. You can say that there is an overlap in the information contained in the two results and this results in a garbage bit. Several reversible adder designs used this ripple structure; *e.g.* reversible *binary-coded decimal* adders have received some interest [142] (Paper A1).

The solution to this problem was presented in 1996 by Vedral *et al.* [148]. They observed that, to do an addition it is not necessary to calculate both the carry and the sum at the same time. If we first calculate the carry in a normal ripple, we can then make a *backwards ripple* where we both uncompute the carry and calculate the sum. This was the first example that shows that it really pays to rethink the problems that we want to solve. However, the cost of not creating garbage was an increase in logic depth. Vedral's *V-shaped adder* was a huge improvement (produces no garbage), but it was not optimal with respect to ancillae and logic depth. In 2005 two papers were published that suggested different improvements to the adder design (in terms of ancilla, gate count and logic depth) [36,146]. See [140] for a detailed description of the adder circuits.

The V-shaped adder is a ripple-carry adder and therefore has large logic depth. We know from conventional logic that it is possible to implement a logarithmic-depth adder at the cost of more logic gates and a more complicated circuit. The first reversible implementations of these adders were embeddings of the carry-lookahead adder [43, 72] and the parallel prefix adder [46], but they all suffered from garbage generation. Based on the techniques from the carry-lookahead adder, Draper *et al.* [45] in 2008 presented a garbage-free logarithmic-depth adder (QCLA)<sup>7</sup>, which added an extra 'look-behind' phase.

We presented another approach to a faster-than-linear reversible adder, the year after, named *ripple-block carry-adder* (RBCA) [140] (**Paper A2**). Basically it is a ripple-carry adder but instead of calculating and rippling one bit at a time, the addition is divided into several smaller block-additions that is performed in parallel. During computation a *carry-correction* phase is added and it is this phase that contains a ripple. When choosing the optimal block-size in relation to the input-size, the adder has a logic depth that is the square-root on the input-size.

When comparing the two, the QCLA in faster than the RBCA, but only significantly when the input is larger than 32 bits. In terms of gate-count the two adders are comparable, but the RBCA uses less ancilla bits. Also the RBCA has a better 'locality' (the gate uses wires that, in the diagram notation, are closer to each other), which can have an impact when the circuit is implemented in the target technology (*e.g.* quantum computer or CMOS).

#### Multiplication

Addition has an intuitive reversible formulation using modular arithmetic and reversible updates. Multiplication, on the other hand, is more difficult to define; mainly because the inverse operation is division. A simple way to define it is to take the embedding from Bennett and save both the multiplicand and the multiplier while still producing the product. This is the trick used by Kawada *et al.* in their (garbage-free) reversible logic implementation of the Karatsuba algorithm [75].

This approach is, however, not satisfying because it expands the amount of information; on the other hand, it is not in general possible to only update the multiplicand and save the multiplier. A possibility (also suggested by Ressler [122]) is to add a remainder, such that mult(A, M, R) = (A\*M+R, M), where  $0 \leq R < M$ . We have started the work towards a reversible logic implementation [14] (**Paper A3**). So far, it works for a certain class of constant multipliers that are equal to  $2^k \pm 1$  for  $k \in \mathbb{N}$ . We expect that this can be extended to general multiplication.

$<sup>^7\</sup>mathrm{The}$  adder was designed with a focus on quantum computing and, thus, the 'Q' in the name. However, it is only implemented with reversible gates.

#### 2.2 Computing Architectures and Instruction Sets

As early as 1965, Reilly and Federighi presented a small instructions set, designed for a one-address machine with accumulator and multiplier-quotient, with the purpose of implementing reversible subroutines [121]. The set is, however, not reversible with respect to our definition; *e.g.* it includes a clearaccumulator instruction, which does not delete information from the overall system but still dissipates energy due to the clear process. The motivation was also not energy efficiency, but a desire to enable code sharing of the implemented subroutines.

The work by Ressler [122] from MIT in 1981 was, however, motivated by energy efficiency. Supervised by Fredkin, he made the design of a conservative logic computer based on a two-address von Neumann architecture. The instruction set contains the basic reversible arithmetic/logic instructions (*e.g.* add, subtract, roll-left and right), and the work contained the idea of using paired-branch instructions and to have both condition and assertion in the conditional. On the other hand, memory could be irreversibly updated and (perhaps most importantly from a program inversion perspective) there was no possibility for inverse execution (uncall).

In 1987 Briggs [23] described a system to control an electronic cricket scoreboard. An important feature of the system was the ability to 'undo' the operations that were performed; a nice feature if the operator made an error. The reverse execution was based on a trace that contained only the minimal information to do the backtracking. Based on this idea of a minimal trace, Cezzar [29] in 1991 presented (and patented) a two-address 'general purpose' machine that can reverse its forward execution.

Having a trace (which would be as long as the number of executed instructions plus amount of deleted information) is, however, a very unsatisfactory solution for a reversible computer. While Cezzar was mainly interested in a computer that could backtrack, Hall [64] designed his improved architecture with reversibility in mind. This ISA does not use a trace, but instead jumps are handled by come-from instructions, which makes it possible to break reversibility.

At MIT, Knight and Younis [165] had been working on a energy efficient logic family (see Section 4) and this implementation technology revived the interest in reversible architectures. Over a few years (ending in 1999) Vieri and Frank developed the reversible von Neumann architecture Pendulum [52,150,151] (formalized in [13]). This architecture was a big step forward. Instead of using only a single special-purpose register for program control (the program counter), the address calculation of the reversible abstract machine relies on three special-purpose registers: program counter, branch register, and *direction bit.* The calculation of the next program counter is then only dependent on the branch register and the direction bit, and the individual instructions cannot directly alter the program counter, but instead only update the branch register and direction bit. Though Pendulum has been fabricated, there is no full detailed description of the actual logic implementation and there is some indication that it is not fully reversible. Firstly, the implementation technology [165] (see Section 4.1 for more details) does not implement the reversible gates, but uses Bennett's method, which results in both the input and output. Secondly, there is no use of the garbage-free V-shaped adder or other arithmetic circuits; Vedral *et al.* [148] is not mentioned by Frank and Vieri, and the rest of the research is from after 1999. Thus, although the abstract architecture of Pendulum (as described by Frank) is reversible, it is likely that the logic implementation is not.

Inspired by the Pendulum architecture and it instruction set, we have designed a fully reversible and garbage-free two-address von Neumann architecture called Bob [141] (Paper B2). It features a locally-invertible instruction set, and the design, including areversible control logic and address calculation, is simple enough to be directly implemented in reversible logic. A central part of the processor design is the arithmetic logic unit (ALU). The conventional ALU has an inherently irreversible functionallity so we have suggested a novel alternative design for a reversible ALU [143] (Paper B1). The design of the ALU in based on the V-shaped adders and follows a strategy that puts all logical operations in sequence and then uses controls to ensure that only the desired operation changes the input. To our knowledge, this is the first garbage-free ALU.

#### 2.3 Multimedia Transformation

Multimedia transforms are an interesting application area for reversible circuits. In small battery-powered devices (*e.g.* smartphones and mp3-players) they are often included as part of an ASIC to reduce power consumption and a key property of many such transforms is that they are information-lossless (and thus invertible). There exist many application areas of such transforms and even the earliest quantum algorithms (including Shor's factorization algorithm [129]) make use of a quantum implementation of the Fourier transform. Also a implementation of the fast Fourier transform in reversible logic has been investigated [130].

Our contributions in this area have focused on implementation of wavelet transforms in reversible logic. Wavelet transforms have also been implemented in quantum computing [50], but our work builds on a paper by Bruekers and van den Enden [24]. Here, they showed a new network structure (the so-called *lifting scheme*) that can be used for perfect inversion and reconstruction of the inputs. This is desired in many transforms and the properties are also a perfect match for reversible implementations. Daubechies and Sweldens show how to factorize wavelet transforms into a lifting scheme [37] and we use this to find the lifting scheme for the linear transform of the *H.264 video encoding* [40] (**Paper C1**). This implementation, however, generates garbage that is caused by a multiplication-by-5.<sup>8</sup> In the latter work we examine other linear transforms that only have multiplications-by-2 [27] (**Paper C2**) and find the associated lifting scheme. (The papers also contain work on CMOS fabrication and testing of the transform from [40]. We shall discuss this in Section 4.)

$<sup>^{8}</sup>$ The design was made before our own garbage-free constant multiplication circuit [14], which solves the problem with multiplication-by-5.

### Computer Aided Design of Reversible Circuits

In Section 2 we discussed the design of reversible logic circuits. All presented circuits (adders, multipliers, and transforms) have a very regular structure, which makes it a lot easier for humans to reason about them. Also, much of the development comes from novel design ideas based on a theoretical insight to the problem. However, not all problems have these properties, so in order to make good realizations of more complex circuits possible, efficient description languages, logic synthesis, and optimization techniques are being developed. Computer aided design of Boolean circuits has been (and is still being) developed (cf. [100]), so in this section we will focus on methods to aid the design of reversible circuits.

#### 3.1 Reversible Logic Synthesis and Optimization

The first approach to reversible logic synthesis is actually a very beautiful example of how mathematics can be related to reversible circuits. Based on work by Rayner and Newman [120], Storme and De Vos [135] used that reversible gates and cascading of these by serial composition forms a group, with the result that it is possible to use the known methods from group theory. Specifically, one of these methods can be used to decompose an arbitrary reversible circuit into a cascade of simpler circuits that only updates one input wire [39, 42]. Each of these simpler circuits can then be interpreted as an *exclusive-or-sum-of-products* (ESOP), which basically is a cascade of controlled-not gates with the number of controls of each gate equals to the number of variables in the products.