## UNIVERSITY OF COPENHAGEN

This thesis has been submitted to the PhD School of The Faculty of Science,

University of Copenhagen

# Automated AI Learning for X-Ray Based Classification

Carl-Johannes Johnsen

carl-johannes@di.ku.dk

Supervisors: Brian Vinter, Kenneth Skovhede, James Avery

December 13th, 2021

#### ACKNOWLEDGEMENTS

First and foremost, I want to thank my three supervisors Brian Vinter, Kenneth Skovhede, and James Avery, for your supervision while having thousands of tasks concurrent to my thesis and for your continued support even from new job positions where you were no longer forced to supervise.

I want to thank the eScience group for your open and helpful nature, always being willing to help and discuss any topic, and providing insightful viewpoints regardless of whether the subject was within your field of research. Even in a semi-disbanded state, you remain helpful.

I want to thank the AXIS partners for always being fast and helpful in providing information, data, and help for both me and the student projects whenever needed.

I want to thank the SPCL group at ETH Zurich for taking me in to be part of your group for such a long time. The quality of your work is impressive, and you have pushed me towards raising my own bar.

I want to thank my army of students for being patient with having me, a junior researcher, as your supervisor. Together we have completed some cool projects that I hope you yourself can be satisfied with - I am at least.

I want to thank my girlfriend, Louise Vedel Jensen, for putting up with my almost constant state of distraction and late-night working, in turn ruining your sleep pattern. Without you, I would forget to eat and sleep, both of which are quite essential.

Finally, I want to thank my friends and family, who have helped me keep my sanity throughout the pandemic and this thesis, always being up for grabbing beers and being patient throughout extended periods of "radio silence" at some points.

#### $A\,B\,S\,T\,R\,A\,C\,T$

Food inspection is a widespread measure for ensuring food quality, contents, and safety. The food inspection industry has deployed cameras and computer vision for a long time since they allow for automatic inspection and evaluation of food quality at a large scale. However, they fail to capture internal defects, which can arise due to natural and unnatural effects. X-ray imaging allows us to inspect the internals of a subject, thus countering the problem. The Adaptive X-ray InSpection (AXIS) project collaborates with multiple partners targeting utilizing X-ray imaging for food inspection. This thesis presents the University of Copenhagen's part of the AXIS project: software for automated AI learning for X-ray-based classification. The main research areas are computer vision, machine learning, and reconfigurable hardware. Computer vision can counter the side-effects of X-ray imaging, resulting in clean images ready for machine learning. In recent years, machine learning has seen a rise in image processing due to its strong predictive power in recognizing patterns in seemingly complex imagery. To keep up with the high-throughput demands of food inspection, we employ reconfigurable hardware, or Field-Programmable Gate Arrays (FPGAs), as these favor pipelines are great at online processing and have been shown to be suitable for machine learning inference. This thesis presents an FPGA-based solution for the preprocessing steps of the X-ray images, a CPU/GPUbased implementation for the machine learning model, along with an outline for an FPGA-based machine learning inference solution. The implementations have had automation in mind, minimizing the required amount of user interaction. This thesis has spawned many student projects that have been supervised throughout the thesis while contributing to the field of reconfigurable hardware through open-source projects seeking to lift the level of abstraction in hardware programming.

## RESUMÉ

Fødevare inspektion er en udbredt foranstaltning til at forsikre fødevare kvalitet, indhold, og sikkerhed. Fødevare inspektions industrien har i lang tid indsat kameraer og datamatsyn, da disse tillader automatisk inspektion og evaluering af fødevare kvalitet i stor skala. Dog kan de ikke fange interne defekter, som kan forekomme på grund af naturlige og unaturlige effekter. Røntgenbilleder tillader os at inspicere et objekts indre og dermed modarbejde disse problemer. Adaptive X-ray InSpection (AXIS) projektet samarbejder med flere partnere om at udnytte røntgenbilleder i fødevare inspektion. Denne afhandling præsenterer Københavns Universitets del af AXIS-projektet: et program til automatisk kunstig intelligens læring til røntgen baseret klassificering. Hovedforskningsområderne har været datamatsyn, maskinlæring, og rekonfigurerbar hardware. Datamatsyn kan modarbejde røntgen sideeffekterne i røntgenbilleder, hvilket resulterer i rene billeder der er klar til maskinlæring. Maskinlæring har set en fremdrift i billede behandling i de senere år, på grund af deres stærke forudsigelses kræft i at genkende mønstre i umiddelbart komplekse billeder. For at kunne følge med de høje datagennemstrømningskrav i fødevare inspektion har vi anvendt rekonfigurerbar hardware, eller Felt-Programmerbar Port-Tabel (FPPT), da disse foretrækker dybe rørledninger (pipelines), er gode til online processering, og har vist sig at være passende til maskinlærings inferens. Denne afhandling præsenterer en FPPT-baseret løsning til præprocessering af røntgenbilleder, en processor/grafikkort-baseret implementering af maskinlærings modellen, samt en opridsning af en FPPT-baseret maskinlærings inferens løsning. Implantationen har haft automatisering i baghovedet for at minimere mængden af bruger interaktion. Denne afhandling har udsprunget mange studenter projekter som er blevet vejledt igennem den her afhandling, samtidig med at den har bidraget til feltet rekonfigurerbar hardware igennem open-source projekter der bestræber sig på at løfte abstraktionsniveauerne i hardware programmering.

# CONTENTS

| I Setting the stage                                         |    |

|-------------------------------------------------------------|----|

| 1 Introduction                                              | 2  |

| 1.1 Automated Inspection                                    | 3  |

| 1.2 The state of modern computing resources                 | 3  |

|                                                             | 4  |

| 1.3.1 Contribution                                          | 5  |

| 2 Outline                                                   | 6  |

| II X-Ray and imaging                                        |    |

| 3 X-ray                                                     | 8  |

| 4 Imaging 1                                                 | 12 |

| 4.1 Super Resolution                                        | 13 |

| 4.2 Seam Carving                                            | 13 |

| 5 X-ray imaging                                             | 16 |

|                                                             | 17 |

| 5.2 Correcting the images                                   | 19 |

| 5.3 Super-resolution on X-ray images                        | 20 |

| 5.4 Extreme seam carving                                    | 21 |

| 5.5 Automated tuning of the setup                           | 21 |

| 6 Subconclusion 2                                           | 24 |

| III Machine Learning                                        |    |

|                                                             | 26 |

|                                                             | 27 |

|                                                             | 27 |

| e                                                           | 28 |

|                                                             | 28 |

| *                                                           | 29 |

|                                                             | 31 |

|                                                             | 32 |

| 9.1 Convolutional Neural Network                            | 33 |

| 9.1.1 Online Inspection of X-ray Images                     | 34 |

| 9.1.2 Automatic classification                              | 35 |

| 9.1.3 Foreign object detection                              | 35 |

| 9.2 Auto Encoders                                           | 37 |

| 9.2.1 Automatic Detection of Foreign Objects                | 38 |

| 9.3 Decision Trees                                          | 40 |

| 9.3.1 Probability of Distress                               | 40 |

| 10 Evaluation 4                                             | 41 |

| 10.1 Accuracy                                               | 41 |

| 10.2 Precision and Recall                                   | 41 |

| 10.3 Receiver Operator Characteristics and Area Under Curve | 42 |

#### contents vi

| 10.4    | Confusion matrix                               | 42       |

|---------|------------------------------------------------|----------|

| 10.5    | Confidence                                     | 43       |

| 10.6    | Diversion and Distribution                     | 43       |

| 11 Det  | ecting floaters in beer                        | 45       |

|         | oconclusion                                    | 49       |

|         |                                                |          |

| IV Fiel | ld-Programmable Gate Array                     |          |

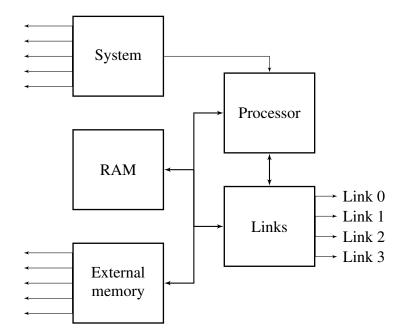

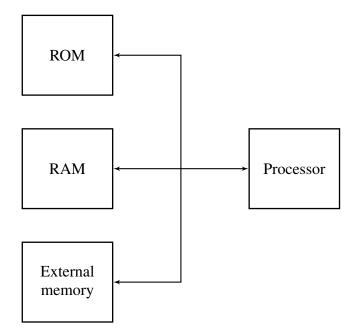

| 13 Ma   | chine Architecture                             | 51       |

| 13.1    | Machine Architecture                           | 51       |

| 13.2    | Central Processing Unit (CPU)                  | 52       |

| 13.3    | Graphics Processing Unit (GPU)                 | 52       |

| 13.4    | Application Specific Integrated Circuit (ASIC) | 53       |

| 13.5    | Field-Programmable Gate Array (FPGA)           | 54       |

| 13.     | 5.1 Register-Transfer Level (RTL)              | 56       |

| 13.     |                                                | 56       |

| 14 Har  | dware Programming Models                       | 58       |

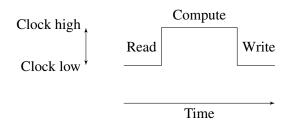

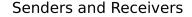

| 14.1    | Synchronous Message Exchange (SME)             | 58       |

| 14.     |                                                | 59       |

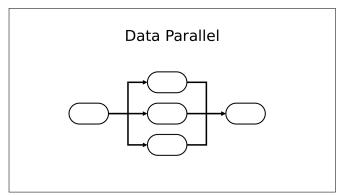

|         | Data-Centric Parallel Programming (DaCe)       | 63       |

| 14.     |                                                | 63       |

| 14.     |                                                | 69       |

| 14.3    | Honerable mentions                             | 74       |

| 14.4    | Case Studies                                   | 76       |

| 14.4    |                                                | 76       |

| 14.     |                                                | 76       |

| 14.     |                                                | 77       |

| 14.     |                                                | 79       |

|         | 6                                              | 79<br>79 |

| 14.     |                                                |          |

| 14.     |                                                | 80       |

| 14.     |                                                | 80       |

| 14.     |                                                |          |

| 14.     |                                                | 81       |

|         | 4.10 Cryptography                              | 83       |

| 15 Sub  | oconclusion                                    | 84       |

| X7 A4   | compation Instruction of V Day images of Food  |          |

|         | comatic Inspection of X-Ray images of Food     | 00       |

|         | aptive X-ray InSpection (AXIS)                 | 86       |

|         | lding the first draft                          | 87       |

| 17.1    | The Data                                       | 87       |

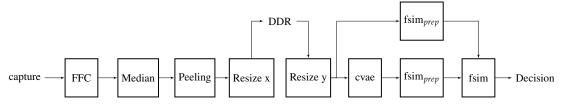

| 17.2    | Preprocessing                                  | 89       |

| 17.3    | Machine Learning Model                         | 90       |

| 17.4    | Detecting Outliers                             | 91       |

| 18 Opt  | imizing for FPGA                               | 94       |

| 18.1    | Flat-Field Correction (FFC)                    | 94       |

| 18.2    | Median filter                                  | 94       |

| 18.3    | Peeling                                        | 95       |

| 18.4    | Image resizing                                 | 96       |

| 18.5    | Normalization                                  | 96       |

| 18.6    | Inference                                      | 97       |

|      | 18.6.          | 1 Activation functions                            | 97  |

|------|----------------|---------------------------------------------------|-----|

|      | 18.6.          | 2 2-dimensional convolution                       | 97  |

|      | 18.6.          | 3 Dense layer                                     | 99  |

|      | 18.6.          | 4 Sample z                                        | 100 |

|      | 18.6.          | 5 Transposed 2-dimensional convolution            | 100 |

|      | 18.6.          | 6 Denormalization                                 | 100 |

| 1    | 8.7 F          | Feature-based Similarity Index Measure            | 100 |

| 1    | 8.8 F          | Final design $\ldots$ $\ldots$ $\ldots$           | 101 |

| 19   | Subco          | nclusion                                          | 102 |

|      | ** *           |                                                   |     |

| VI   | Wrap           |                                                   |     |

| 20   | Future         | e Work                                            | 104 |

| 21   | Concl          | usion                                             | 105 |

| VII  | Biblic         | ography                                           |     |

|      | liograp        |                                                   | 107 |

| DIU  | nograp         | lly                                               | 107 |

| VIII | Apper          | ndices                                            |     |

| А    | Paper          | S                                                 | 114 |

| А    | .1 F           | Published papers                                  | 114 |

|      | A.1.1          |                                                   |     |

|      | A.1.2          |                                                   |     |

|      |                | matical Proofs                                    | 136 |

|      | A.1.3          |                                                   |     |

|      | A.1.4          |                                                   |     |

| А    |                | ces                                               |     |

| В    | Projec         |                                                   | 164 |

|      | v              | Master Thesis'                                    |     |

| Б    | в.1.1          | High Throughput Image Processing in X-Ray Imaging |     |

|      | в.1.2          |                                                   |     |

|      | B.1.3          |                                                   |     |

|      | в.1.4          | Automating Classification in Food Inspection      |     |

|      | в.1.4          |                                                   |     |

|      | в.1.5<br>в.1.6 |                                                   |     |

|      | в.1.0<br>в.1.7 |                                                   | 1/2 |

|      | D.1./          | X-Ray Them                                        | 172 |

|      | в.1.8          | •                                                 |     |

|      |                |                                                   |     |

|      | в.1.9<br>в.1.1 | e e                                               |     |

|      | в.1.1<br>в.1.1 |                                                   |     |

|      |                |                                                   |     |

|      | B.1.1          |                                                   |     |

| -    | B.1.1          | 8 8 5                                             |     |

| В    |                | Bachelor Thesis'                                  |     |

|      | в.2.1          | Probability of Distress                           |     |

|      | в.2.2          |                                                   | 182 |

|      | в.2.3          | e                                                 | 105 |

|      | _              | Hollow Heart                                      |     |

|      | в.2.4          | 5                                                 |     |

|      | в.2.5          | Occam to Go Translator                            | 186 |

|   | в.2.6   | Cryptographic Library for FPGAs                               | 187 |

|---|---------|---------------------------------------------------------------|-----|

| В | .3 Proj | ects in Practice                                              | 188 |

|   | в.3.1   | A Generic Buffer Management for High Performance FPGA Systems | 188 |

|   | в.3.2   | An Object Store for FPGA                                      | 189 |

|   | в.3.3   | PyBoy Rewind                                                  | 190 |

|   | в.3.4   | Emulation of the Game Boys Link Cable                         | 191 |

|   | в.3.5   | Cloud Storage Solution for Industrial Camera                  | 192 |

| С | Hardwar | e                                                             | 193 |

# LIST OF FIGURES

| 1  | The electromagnetic spectrum at different frequencies and wavelengths.               | 8  |

|----|--------------------------------------------------------------------------------------|----|

| 2  | Linear attenuation coefficient between hay and a needle.                             | 9  |

| 3  | X-ray filtered bremsstrahlung spectrum simulation using Tungsten anode               | 10 |

| 4  | Visualization of the cone effect that arises from having a single point source       | 10 |

| 5  | Halo effect on an X-ray image                                                        | 11 |

| 6  | Visualization of how the low-resolution domain relates to the high-resolution domain | 13 |

| 7  | Images showing the process of super-resolution.                                      | 14 |

| 8  | Seam carving applied to an orange with a needle inside.                              | 14 |

| 9  | Closeup of how the camera is shieled by using mirrors.                               | 17 |

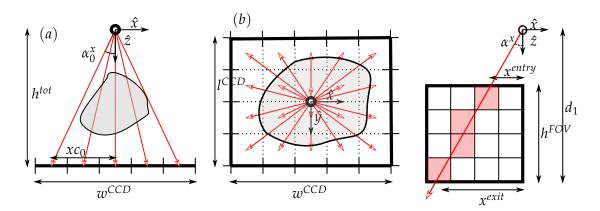

| 10 | Visualization of the X-ray simulator setup.                                          | 18 |

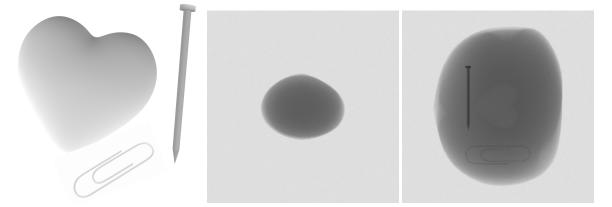

| 11 | Output from the X-ray simulator.                                                     | 18 |

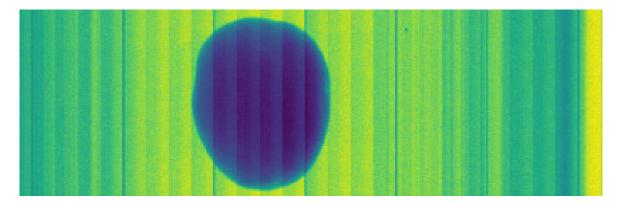

| 12 | Raw X-ray image of a potato                                                          | 19 |

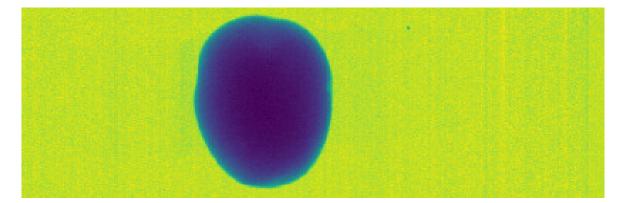

| 13 | Corrected X-ray image of a potato                                                    | 20 |

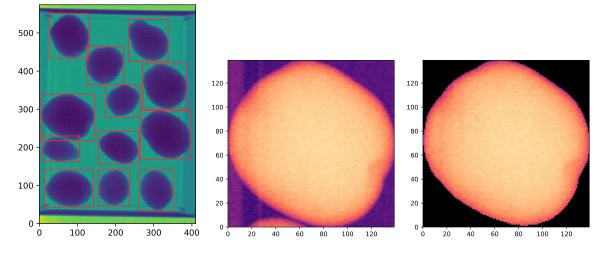

| 14 | The three major steps of the ROI algorithm                                           | 20 |

| 15 | Super-resolution applied to X-ray images of a circuit board.                         | 21 |

| 16 | X-ray scans of different foods with varying levels of complexity.                    | 22 |

| 17 | X-ray images of plums at a varying voltage and ampere                                | 23 |

| 18 | Effects of blurring an X-ray image of meat with a paperclip                          | 28 |

| 19 | Histogram and segmentation of an X-ray image of meat.                                | 29 |

| 20 | Gamma correction applied to an X-ray image of meat.                                  | 30 |

| 21 | Different histogram equalizations on an X-ray image of meat.                         | 30 |

| 22 | Application of different resizing approaches to an X-ray image                       | 31 |

| 23 | Morphology operations used to clean the mask after thresholding                      | 31 |

| 24 | Render of a single perceptron                                                        | 32 |

| 25 | A fully connected deep neural network                                                | 33 |

| 26 | Overview of how the convolution operation is applied                                 | 34 |

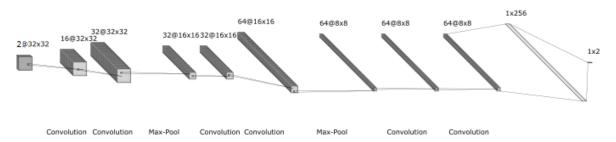

| 27 | Full overview of a Convolutional Neural Network (CNN)                                | 34 |

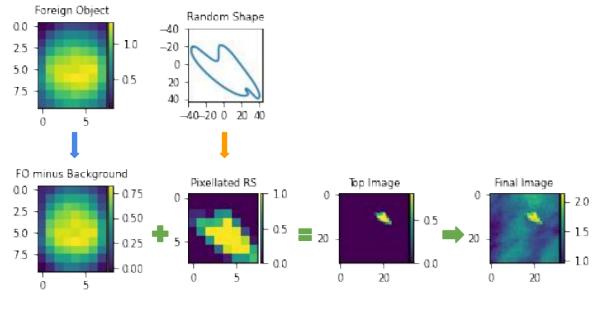

| 28 | Overview of the process of adding artificial foreign objects                         | 36 |

| 29 | Architecture of the resulting CNN for detecting foreign objects in meat              | 36 |

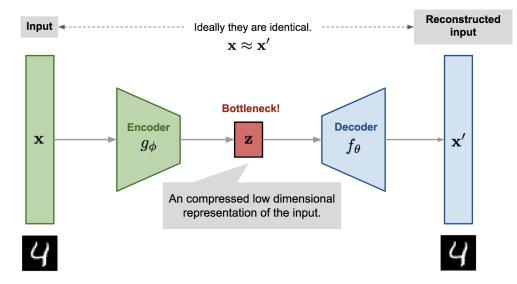

| 30 | Coarse architecture of the Convolutional Auto Encoder (CAE) model                    | 37 |

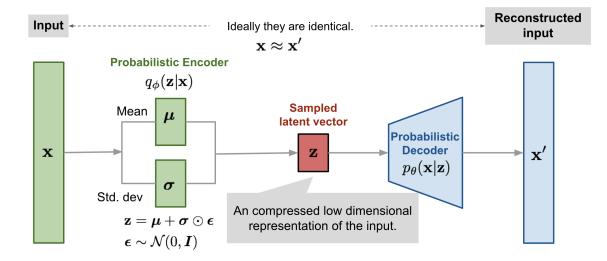

| 31 | Coarse architecture of the Convolutional Variational Auto Encoder (CVAE) model       | 38 |

| 32 | Chocolate after being reconstructed by a CVAE.                                       | 39 |

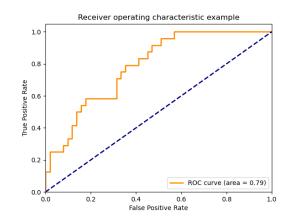

| 33 | Example Receiver Operator Characteristics (ROC) curve                                | 42 |

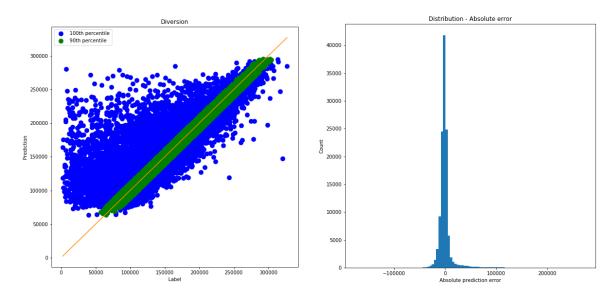

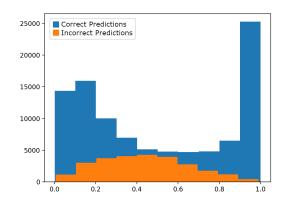

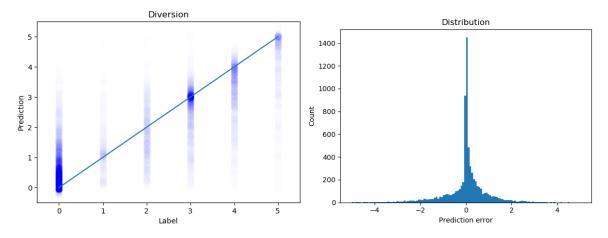

| 34 | Diversion plot of a regressor.                                                       | 43 |

| 35 | Distribution plot of a regressor.                                                    | 43 |

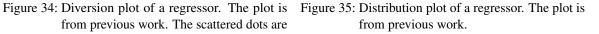

| 36 | Confidence plot of a classifier.                                                     | 44 |

| 37 | The machine setup for capturing the beer videos                                      | 46 |

| 38 | Raw image from a beer video sample                                                   | 47 |

| 39 | Image from a beer video sample with enhanced floaters                                | 47 |

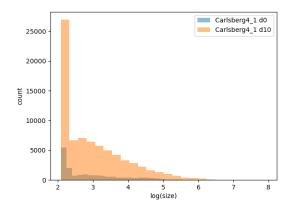

| 40 | Histograms of floater sizes, computed from an image of beer                          | 47 |

| 41 | Diversion and Distribution plots of the trained brewery model                        | 48 |

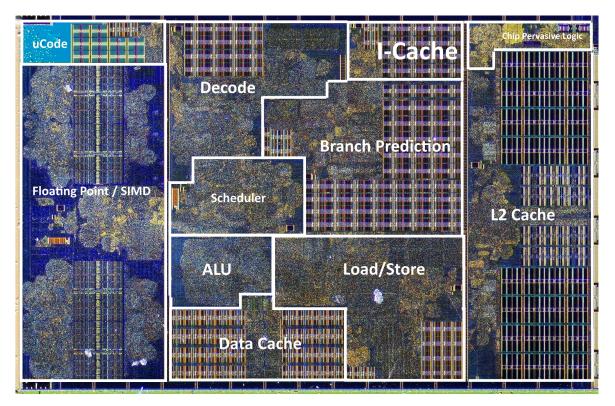

| 42 | Die shot of a Central Processing Unit (CPU)                                          | 53 |

| 43 | Coarse-grain block diagram of a CPU and a Graphics Processing Unit (GPU)                 | 54 |

|----|------------------------------------------------------------------------------------------|----|

| 44 | Block diagram of the conceptual Field-Programmable Gate Array (FPGA)                     | 55 |

| 45 | The simulation cycle of an Synchronous Message Exchange (SME) simulation                 | 59 |

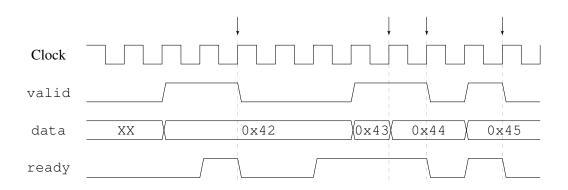

| 46 | Waveform of four streaming Advanced eXtensible Interface (AXI) transactions              | 65 |

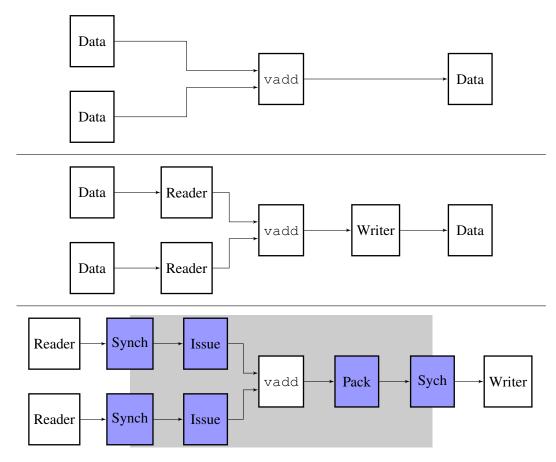

| 47 | Stateful DataFlow multiGraphs (SDFGs) depicting the general transformation to a stream-  |    |

|    | ing application.                                                                         | 67 |

| 48 | Block diagram showing the inner histogram implementation.                                | 68 |

| 49 | Block diagram of the internal Register-Transfer Level (RTL) code for AXPY                | 69 |

| 50 | Waveform depicting the multi-pumping optimization with $M = 2, v = 2$ . Image from [50]. | 71 |

| 51 | Block diagram for a vector addition computation core.                                    | 72 |

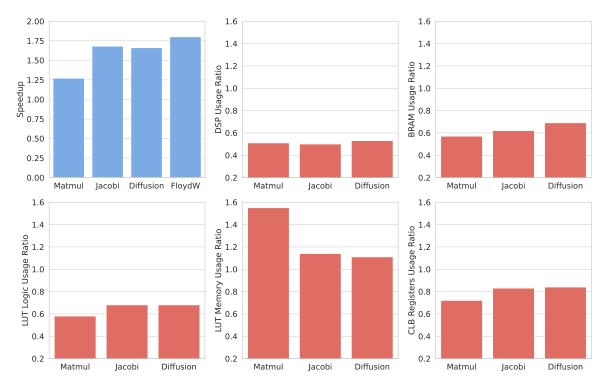

| 52 | Performance and resource-saving overview from the multi-pumping evaluation.              | 75 |

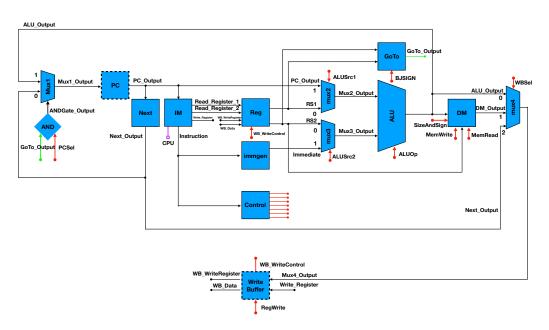

| 53 | Block diagram of the RISC-V processor.                                                   | 77 |

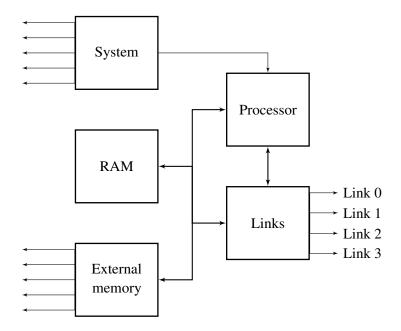

| 54 | Block diagram of the SME Transputer. Image from [64]                                     | 78 |

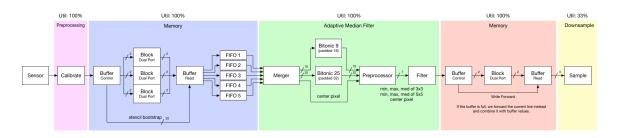

| 55 | Final pipeline design for Troels' FPGA implementation. Image from [17]                   | 79 |

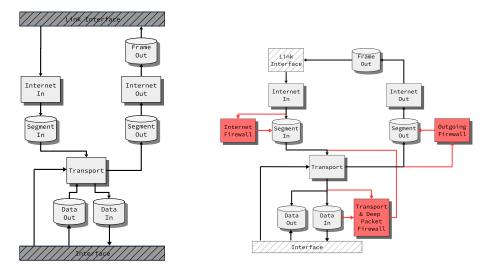

| 56 | Final design for the Transmission Control Protocol / Internet Protocol (TCP/IP) and      |    |

|    | firewall SME projects                                                                    | 79 |

| 57 | Block design of the firewall.                                                            | 80 |

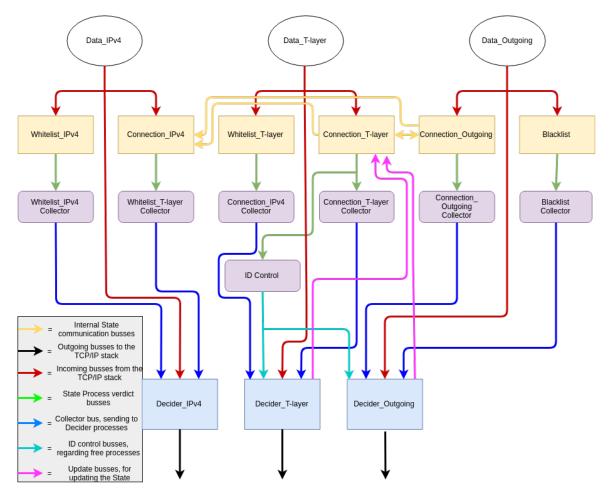

| 58 | The block diagram of the overall feed-forward neural network. Image from [74]            | 81 |

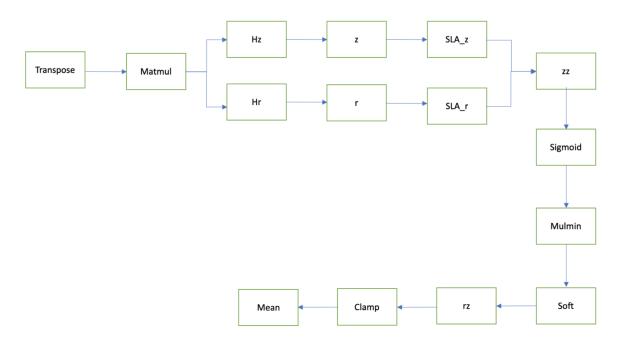

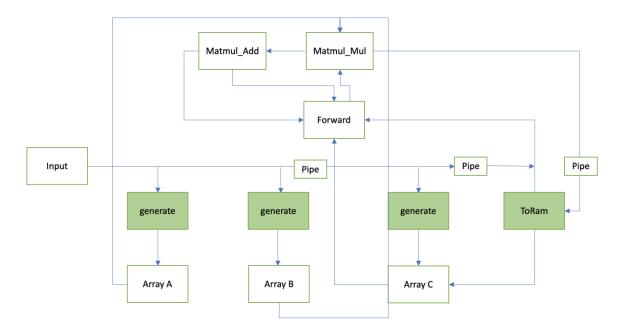

| 59 | The block diagram of the internal structure of the Matmul block.                         | 82 |

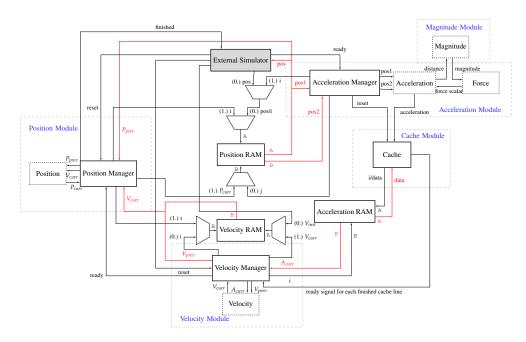

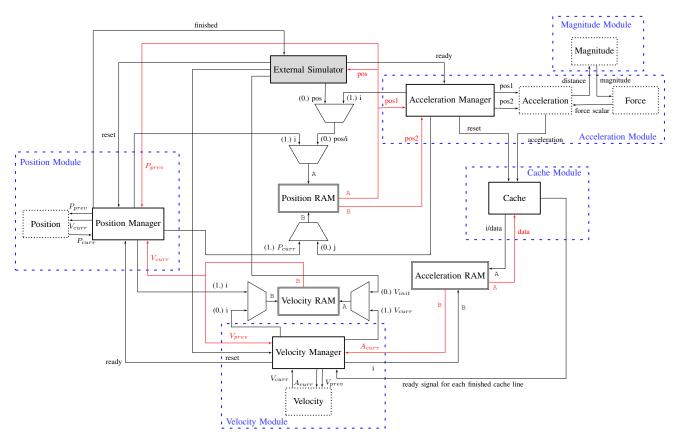

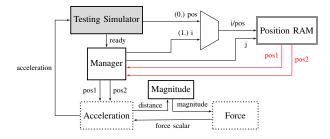

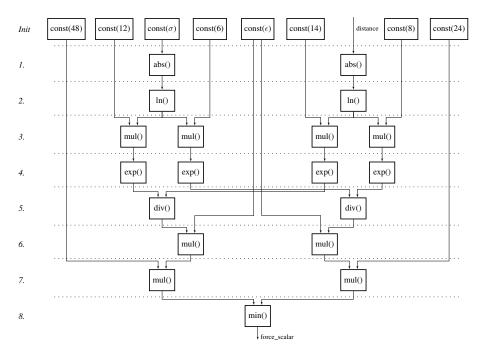

| 60 | Block diagram of the SME network computing molecular dynamics simulation.                | 82 |

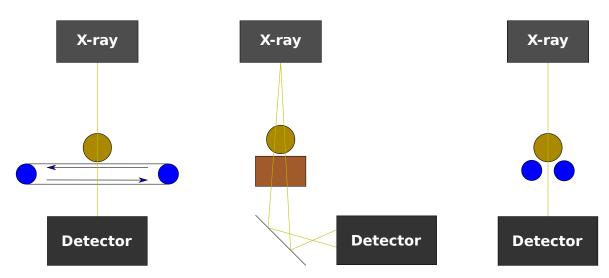

| 61 | High-quality schematics of the different X-ray capturing setups.                         | 88 |

| 62 | Four raw X-ray images captured by the new line scanner setup.                            | 88 |

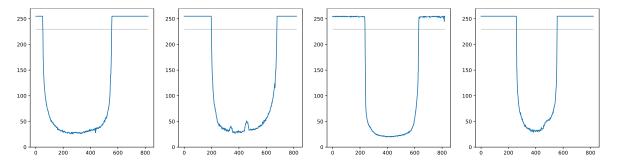

| 63 | Lines extracted from the new potato images.                                              | 89 |

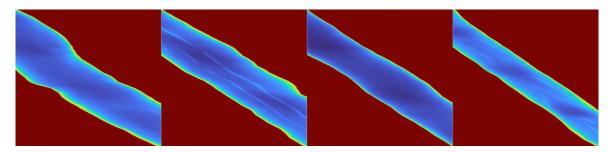

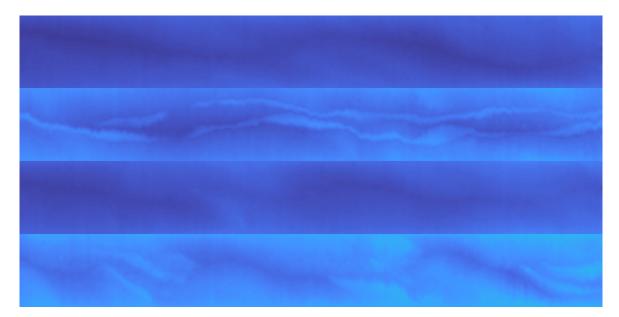

| 64 | Four X-ray images after being peeled.                                                    | 90 |

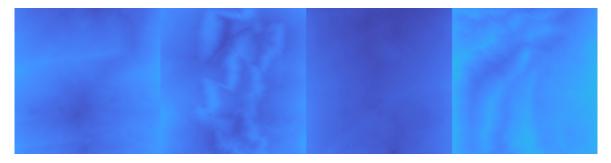

| 65 | Four X-ray images after being seam carved.                                               | 90 |

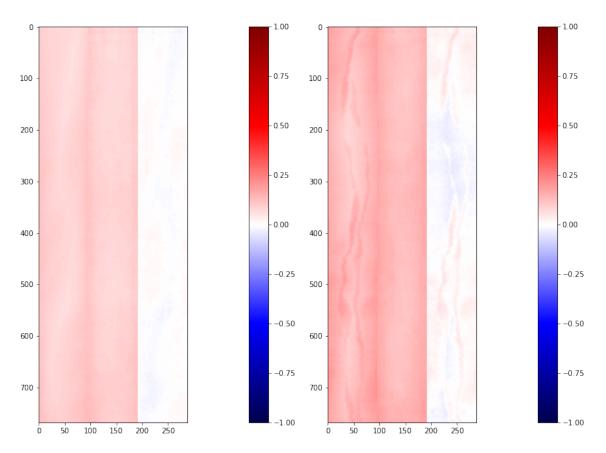

| 66 | Comparison of the reconstruction of the peeled potatoes by the Machine Learning (ML)     |    |

|    | model.                                                                                   | 91 |

| 67 | Histograms of the sample distribution when using Structural Similarity Index Measure     |    |

|    | (SSIM) and Feature-based Similarity Index Measure (FSIM).                                | 92 |

| 68 | ROC curves and Area Under Curve (AUC) score comparing SSIM and FSIM.                     | 93 |

| 69 | Histogram showing the distribution of the four classes using FSIM.                       | 93 |

| 70 | Distributions of a 5-fold cross validation using the CVAE and FSIM.                      | 93 |

| 71 | Block diagram of Flat-Field Correction (FFC).                                            | 95 |

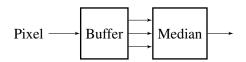

| 72 | Block diagram showing the median filter.                                                 | 95 |

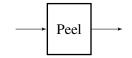

| 73 | Block diagram of the peeling process.                                                    | 95 |

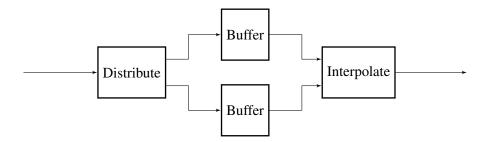

| 74 | Block diagram for resizing one line of an image.                                         | 96 |

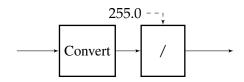

| 75 | Block diagram for normalization.                                                         | 96 |

| 76 | Block diagrams for the implementation of the activation functions.                       | 98 |

| 77 | Block diagram for a two-dimensional convolution.                                         | 99 |

| 78 | Overview of an Linear-Feedback Shift Register (LFSR) implementation.                     |    |

| 79 | Block diagram for denormalization.                                                       |    |

| 80 | Overview of the components of the final solution connect.                                |    |

# LIST OF TABLES

| 1  | X-ray generator specifications                                     | 9  |

|----|--------------------------------------------------------------------|----|

| 2  | Chemical composition of a needle made of hardened carbon steel     | 9  |

| 3  | Chemical composition of hay.                                       | 9  |

| 4  | Overview of the different foods scanned for the seam carving paper | 23 |

| 5  | Best results from the potaNet thesis [23]                          | 35 |

| 6  | Specification and results of potaNet.                              | 35 |

| 7  | Overview of the best performing CNNs from Topic's thesis           | 35 |

| 8  | Proposed CVAE architecture.                                        | 39 |

| 9  | Overview of a confusion matrix                                     | 43 |

| 10 | Resource utilization and frequency of the SME Transputer.          | 77 |

| 11 | Performance metrics of the Occam Go transpiler                     | 78 |

#### ACRONYMS

ALU Arithmetic Logic Unit. 52, 56 AMBA Advanced Microcontroller Bus Architecture. 64, 94 AMF Adaptive Median Filter. 19, 94, 95 ANN Artificial Neural Network. 3, 26, 32–34, 37, 40, 46, 49, 100, 105 API Application Programming Interface. 62 ASIC Application-Specific Integrated Circuit. 4, 53–55, 84 AST Abstract Syntax Tree. 59–62 AUC Area Under Curve. x, 38, 40, 42, 92, 93, 102 AXI Advanced eXtensible Interface. x, 64, 65, 67, 70, 73, 94, 95, 97, 98 AXIS Adaptive Xray InSpection. 4–6, 24, 26, 49, 86, 87, 102 **BLAS** Basic Linear Algebra Subprograms. 63, 67 BRAM Block Random-Access Memory (RAM). 56, 62, 70, 79, 94, 96, 99 CAE Convolutional Auto Encoder. ix, 37 **CCD** Charge Coupled Device. 12 CGRA Coarse-Grained Reconfigurable Arrays. 76 CLAHE Contrast Limited Adaptive Histogram Equalization. 29, 30 CMOS Complementary Metal Oxide Semiconductor. 12 CNN Convolutional Neural Network. ix, xi, 3, 33–36, 49, 90, 105 **CPU** Central Processing Unit. ix, x, 3, 4, 51–56, 62, 64, 67, 81, 83, 84, 87, 100 CSP Communicating Sequential Processes. 58, 59, 76, 77 CSV Comma-Separated Values. 59 CVAE Convolutional Variational Auto Encoder. ix-xi, 37-39, 49, 91-93, 97, 100, 102, 104, 105 **DaCe** Data-Centric parallel programming. 5, 63, 64, 66, 67, 71, 73, 76, 84, 104, 105 **DDoS** Distributed Denial of Service. 80 **DDR** Double Data Rate. 54, 96 **DSL** Domain Specific Language. 74, 76 **DSP** Digital Signal Processor. 56, 70, 74 **DT** Decision Tree. 40 ETH Eidgenössische Technische Hochschule. 63 FDR Failures-Divergences Refinement. 59 FF Flip-Flop. 56, 70

FF Filp-Filop. 36, 70

FFC Flat-Field Correction. x, 19, 89, 94, 95, 102

FFT Fast Fourier Transform. 100

FIFO First In First Out. 79

FPGA Field-Programmable Gate Array. x, 4, 6, 51, 54–56, 58, 60, 62–66, 69–71, 74, 76, 79–81, 84, 94, 95, 97, 100, 102, 104, 105

FPN Fixed-Pattern Noise. 19

FPR False Positive Rate. 42

FSIM Feature-based Similarity Index Measure. x, 92–94, 100–102

**GBDT** Gradient Boosted Decision Tree. 40 **GPU** Graphics Processing Unit. x, 3, 4, 51–55, 84, 100

HBM High Bandwidth Memory. 70

HDL Hardware Description Language. xiii, 56

HE Histogram Equalization. 29, 30

HLS High-Level Synthesis. 55, 56, 58, 63–66, 69–71, 73, 75, 76, 84

HPC High-Performance Computing. 84

IL Intermediate Language. 61, 62

IP Intellectual Property. 54, 55, 62, 63, 69, 72, 73

IR Intermediate Representation. 55, 63, 71

IRWSR Iterative Re-Weighted Super-Resolution. 13, 14

**LFSR** Linear-Feedback Shift Register. x, 100 **LUT** LookUp Table. 56, 70, 74

MAE Mean Absolute Error. 46, 48

MFSR Multi-Frame Super-Resolution. 13

ML Machine Learning. x, 3–6, 20, 26–29, 32, 35, 40, 45, 46, 48, 49, 86, 89, 96, 97, 102, 104, 105, 169

MSE Mean Squared Error. 37, 104

**ONNX** Open Neural Network eXchange. 63, 104 **OpenCL** Open Computing Language. 64

PCA Principle Component Analysis. 37PCIe Peripheral Component Interconnect Express. 54PE Processing Element. 75

**RAM** Random-Access Memory. xii, xiii, 54, 56, 94, 96 **RMSE** Root Mean Square Error. 46 **ROC** Receiver Operator Characteristics. ix, x, 42, 92, 93 **ROI** Region Of Interest. 19, 20, 28, 46, 89, 95 **RTL** Register-Transfer Level. x, 55, 56, 58, 63–67, 69, 71, 73, 75, 76, 84

SDFG Stateful DataFlow multiGraph. x, 63, 66, 67

SDRAM Synchronous Dynamic RAM. 54

SIMD Single Instruction, Multiple Data. 4, 73

SME Synchronous Message Exchange. x, xi, 5, 58–62, 75–84, 105

SPCL Scalable Parallel Computing Laboratory. 63, 66

SSIM Structural Similarity Index Measure. x, 38, 91–93, 102

TCL Tool Command Language. 63 TCP/IP Transmission Control Protocol / Internet Protocol. x, 79, 80 TPR True Positive Rate. 42 TPU Tensor Processing Unit. 4, 180

VHDL Very High-Speed Integrated Circuit (VHSIC) Hardware Description Language (HDL). 56, 59, 62, 63, 75

VHEIC V = 11 to 12 to

VHSIC Very High-Speed Integrated Circuit. xiii, 56

XML eXtensible Markup Language. 64 XOR eXclusive OR. 100 Part I

# SETTING THE STAGE

## INTRODUCTION

The food industry produces vast amounts of food every day, which goes through rigorous quality control. This quality control is primarily to ensure that the product is safe for human consumption and meets the high standards imposed by the average consumer. For example, everyone has had the experience of discarding certain vegetables due to them being misshapen or discolored. We define defects such as these as being mild defects. A product with a mild defect might not render the entire product unusable but rather render it unattractive. On the other end of the scale, we have hazardous defects, which constitute unsafe defects.

An example of this could be pieces of metal, which come from a broken blade slicing meat into cold cuts and could be fatal if consumed. While some cases occur from natural events, they can also occur deliberately, such as the needles in strawberries case [1]. This case was sabotage, where a person targeted a strawberry farmer by putting needles in strawberries. As a result, the farmer had to recall a whole season's harvest, thus losing income.

While quality control through manual inspection is trivial, it quickly becomes infeasible once food production is scaled up. E.g., a potato farmer can produce several tons of potatoes an hour during harvesting. Therefore, it is crucial that inspection happens as fast as possible, minimizing the time spent, to not waste resources or potential income. These defects can occur at every step of the production pipeline: growing, harvesting, packaging, and shipping. As such, inspection should not be limited to one step of the pipeline and could be done at multiple stages until right before selling the product. The defects in food occur both externally and internally. External defects can be detected using visual camera inspection, which the industry currently employs. However, this does not capture internal defects, such as the metal needles inside the subjects. We can "look inside" the scanned subject by using X-ray imaging. For example, it is a widespread technique used for internal inspection without "opening" the subject as long as the defects consist of different density materials compared to the scanned subject. A density difference will cast prominent shadows on the resulting image, allowing a trained expert to diagnose potential causes and treatments. While X-ray is harmful to living tissue through prolonged exposure, it does not affect living tissue for short bursts of exposure. Furthermore, foods have shown no signs of degradation or carrying any hazardous amounts of radiation following being scanned by X-ray [2].

This thesis investigates the steps required for automated food inspection using X-ray imaging. Once we establish a baseline for achieving this functionally, we will focus on optimizing the baseline to keep up with the high throughput requirements found in the industry.

#### 1.1 AUTOMATED INSPECTION

A popular way to automate visual inspection is through cameras and computer vision. A camera captures a photo by exposing its photocells to light that reflects off a surface. The number of photons hitting the photocell determines the intensity of a pixel. This intensity is then translated into a digital signal, representing the number of photons that hit the photocell during the exposure period. Multiple photocells are employed to produce color images, where each photocell captures photons within a particular wavelength. X-ray images are captured much like regular images, but instead of capturing light reflected off a surface, X-ray photons penetrate matter and hit a substrate called a scintillator. When hit by photons in the X-ray spectrum, this substrate gets excited, emitting photons in the visible spectrum. This emitted light is what is the camera captures during X-ray imaging. Generally, X-ray imaging uses two different types of camera: an area scanner or a line scanner. An area scanner is a 2-dimensional grid of photocells, which make up an image. A line scanner is a single row of photocells, which only captures a single image row. Line scanners are more prevalent in X-ray imaging than area scanners because they are cheaper and often have a higher capture rate. This higher capture rate is a side effect of having fewer photocells to drain during capture than an area scanner.

The field of computer vision covers the act of programmatically having the computer understand the context in imagery or video. In recent times, Machine Learning (ML) has had a rise in popularity for image recognition problems due to the ease of expressing the problem, large amounts of data available, the exponential rise in computational resources through time, and finally, the predictive power of ML. In ML, one "trains" a *machine* model to recognize a pattern through *learning*, achieved by providing a large dataset that contains the pattern. Roughly speaking, ML incorporates two main approaches: supervised and unsupervised learning. In unsupervised learning, the data "speaks for itself," and the model attempts to derive a pattern purely from the data. In supervised learning, the data features corresponding labels, and the model attempts to match this labeling during training by predicting the label based on the data. In both cases, an oversimplification is that the model is a many-dimensional function with many tunable parameters that are tuned during training to provide the best *fit* to the data.

The image recognition ML models have become more resilient at detecting patterns at the same level as humans, at least for specific problems, such as the classic example with handwritten digits [3]. The winning strategy for this example has been the Convolutional Neural Network (CNN); an extended version of the Artificial Neural Network (ANN) that has preceding convolutional layers for extracting the features of an image. The model's complexity defines a model's expressive power, enabled by the computing resources available in modern machines. However, the demand keeps rising for even more complex models, introducing higher demands for more computing resources.

#### 1.2 THE STATE OF MODERN COMPUTING RESOURCES

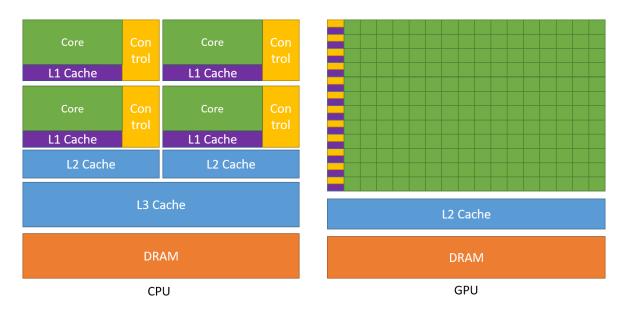

Central Processing Units (CPUs) are excellent due to their versatility and focus on generality. CPUs have become faster and more numerous, with eight processing cores commonly available in a chip. However, most chip area constitutes speculative execution and control flow rather than computational power. While this is great for most tasks handled by a computer, it is not so great for machines that continuously only handle one particular problem, such as ML inference in an inspection pipeline.

Graphics Processing Units (GPUs) takes a step towards trading generality for computational power. GPUs consist of thousands of cores set up in a grid-like fashion. These chips favor parallel problems as each core is weak compared to a standard CPU core. This weakness comes to light in problems that feature lots of branching and dynamic executions. However, the GPUs are overall computationally stronger due to the sheer amount of execution cores and the focus on memory access patterns. These cores specialize in vector processing: doing the same operation on multiple data elements. This type of execution is known as Single Instruction, Multiple Data (SIMD). By expressing matrix computations as a series of SIMD operations, GPUs become very efficient at doing matrix computations.

The final step in the generality trade-off ladder is custom circuitry where the user is in complete control – for better or for worse. Nevertheless, the potential gains here are significant since only the parts that the user deems necessary remain. These are known as Application-Specific Integrated Circuits (ASICs) and are the superset of all integrated circuits. However, in the context of this thesis, we will limit the term ASIC to integrated circuits, which focus on solving single tasks. Examples of ASICs focusing on ML are Tensor cores [4] found in newer NVIDIA GPUs, Tensor Processing Unit (TPU) [5] developed by Google, and Neural Engines found in the new Apple M1 chips [6].

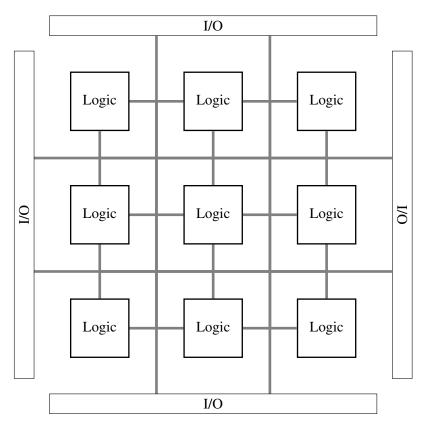

The middle ground between generality and specificity is the Field-Programmable Gate Array (FPGA), also known as reconfigurable hardware. Where the ASIC is unmodifiable after production, an FPGA focuses on reconfigurability. Conceptually, an FPGA consist of a grid of logic gates connected through a user-defined interconnect. Thus, the user defines their hardware model by specifying how these gates are connected, resulting in a semantically equivalent circuit compared to fully purposed hardware.

However, reconfigurability comes at a price because the connections within the FPGA are not as fast as purpose-built hardware connections. As such, FPGAs cannot reach such aggressive clock rates as the ASICs, giving them orders of magnitude worse performance than ASICs. Compared to CPUs and GPUs, FPGAs excel in either deeply pipelined or very custom problems. For example, GPUs are purpose-built for vector operations, making this problem hard to beat with FPGAs. However, FPGAs are best if we compare them using more exotic problems, such as low precision math or control-oriented problems. Furthermore, they are generally more stable than CPUs and GPUs, as the reduced complexity also reduces the probability of an error occurring. Finally, cutting away generality also reduces power consumption, as the power flows through a reduced number of transistors and connections.

#### 1.3 ADAPTIVE X-RAY INSPECTION

The Adaptive Xray InSpection (AXIS) project aims to solve automated food inspection using X-ray imaging. It is a collaborative project between four partners; the University of Copenhagen, Newtec, Qtechnology, and Magnatek.

- NEWTEC has a long history of building industrial machines for quality assurance, weighing, packaging, and sorting food products. Their primary technique is visual inspection through cameras to look for defects for quality assurance. They will be building the machine, which will assemble the three other deliverables into a single product. They are also looking into finding the right scintillator, which will have suitable properties for food inspection.

- QTECHNOLOGY is a daughter company of Newtec, which specializes in camera technology. Their main product is a camera and computer consisting of a CPU, GPU, and FPGA, all built into a single package. It is the driving force of Newtec's visual inspection part of their machines. They will be delivering the camera for the AXIS project.

MAGNATEK is a company that produces high-frequency X-ray sources, which a wide array of machines employ, including food inspection and sorting. They will be delivering the X-ray source for the AXIS machine.

The final piece of the AXIS puzzle is the software part delivered by the University of Copenhagen, an automated solution for building ML models for food inspection, which live up to the industry's high throughput requirements. This thesis investigates the different ways of achieving this, both functionality- and performance-wise. The final implementation is based on the findings from supervising multiple student projects that have sprung as an effect of this thesis and the research done in the various fields.

#### 1.3.1 Contribution

This thesis has contributed to open-source projects in the field of programming models for reconfigurable hardware: Synchronous Message Exchange (SME) and Data-Centric parallel programming (DaCe). SME has been improved quality-wise while seeing new abstractions enabling software programmers to delve into the world of hardware development by leveraging modern development tools and language features through compositional process isolation abstractions. DaCe allows the developer to target multiple platforms from a high level of abstraction. This thesis has improved the expressibility of DaCe by providing tighter integration of low-level implementations in this higherlevel representation, allowing the hardware-specific optimizations, such as our automatically applied multi-pumping optimization.

A big problem in supervised ML is the need for a complete representation of the sample space. This thesis proposes a semi-supervised approach to the classification problem, where we train a model purely on one class of samples, gaining a model that, without ever seeing samples from other classes, can distinguish between "good" and everything else. This proposed model can further be implemented as a pipelined streaming application, keeping up with the high-throughput requirements of food inspection.

The open-source contributions have been made on Github, by the account carljohnsen [7].

# OUTLINE

This thesis focuses on the University of Copenhagen's deliverable to the AXIS project, a program for automated food inspection using X-ray imaging. From a top-level view, the thesis consists of five parts, with Part i being this introduction.

One of the critical features of the AXIS project is the use of X-ray imaging. Part ii will describe the principles behind X-ray and imaging in order to describe how to capture X-ray images. These concepts should help the reader build intuition regarding the challenges of X-ray imaging. The research contribution of this part is in general image processing, explicitly targeting the challenges of X-ray imaging. This thesis is a computer science thesis, not a physics thesis, so the physics described will be conceptual.

Part iii presents some core ML concepts, such as how we build and evaluate a model. We will cover the research we have investigated during this thesis laying the foundation for our later choice of model. The research focus has been on the application of the ML field, especially preprocessing, different model architectures, and model evaluation techniques.

Part iv starts by describing general machine architecture to lay a conceptual foundation for the reader and to motivate the use of FPGAs. As high-throughput is a requirement for the final product, most of the work put into this thesis has been in accelerators, specifically reconfigurable computing. The research has focused on programming models for FPGAs, seeking to lift the abstraction of hardware design into the field of software development to allow for a broader population of hardware developers.

Finally, Part v will be combining the knowledge from the previous parts to outline the final product; a low-power, high throughput, and stable classifier.

This thesis has spawned many sub-projects whose relevance and results we cover throughout the thesis whenever relevant, along with Appendix B, covering them in full.

Part II

# X-RAY AND IMAGING

#### X - R A Y

This chapter will cover the physics of X-rays to build a foundational understanding of how we capture the images. We can counter some of these effects, but some are just a natural outcome of physics. As this Ph.D. thesis is in computer science, not physics, the theory will be on a conceptual level.

Light consists of photons oscillating at some wavelength, and they belong to a specific class of light depending on this wavelength. X-ray is one of these classes of light, which reside within a particular wavelength. Specifically, X-ray lies within 0.01 to 10 nanometers (*nm*), whereas the more well-known visible light is within 380 to 700 *nm*. As such, the X-ray has a much shorter wavelength compared to visible light. Given the constant speed of light, *c*, then the wavelength,  $\lambda$ , is directly tied to the frequency, *f*, of the photons:

$$\lambda = \frac{c}{f} \tag{1}$$

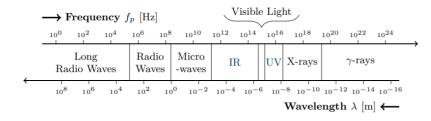

This relation translates into: the shorter the wavelength, the higher the frequency. Furthermore, higher frequencies translate into higher energies. High energy is what gives the photons their penetrative properties. Figure 1 shows the different light classes, wavelengths, and corresponding frequencies.

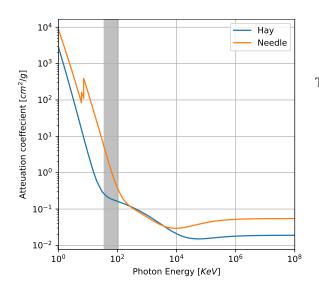

When X-ray photons interact with matter, the photons will be absorbed, slowed, or diverted, depending on the photons' energy and the matter's density. Attenuation curves describe how a particular material will absorb a beam of photons at a particular energy. This curve shows the probability of an interaction between the beam and material. Thus, the larger the attenuation coefficient, the more likely the material will absorb the beam.

One possible application for attenuation curves is choosing the energy that maximizes contrast on the final image. For example, imagine having to locate a needle in a haystack. We consider the chemical composition of a needle as specified in Table 2 and of hay as specified in Table 3. From the

Figure 1: The electromagnetic spectrum given different frequencies and wavelengths that are related by Equation (1). Image from [8].

Figure 2: Log-log plot of the linear attenuation coefficient between hay and a needle. The gray area shows the spectrum achievable by the X-ray source described in Table 1.

Table 1: X-ray generator, numbers taken from the datasheet [9]. Note that the source is rated to 500W and 100kV, but during its warm up phase, it was possible to push it a bit outside its recommended working limits.

| Name          | Value                   |

|---------------|-------------------------|

| Manufacturer  | Spellman                |

| Model         | XRBHR100 monoblock      |

| Voltage range | 35-105kV                |

| Current range | 0.35-7.5 mA (35-70 kV)  |

|               | 0.35-5.0 mA (71-105 kV) |

| Max power     | 525 W                   |

Table 2: Chemical composition of a needle made of hard-<br/>ened carbon steel. Values from [10].

| Material        | Amount |   |          |

|-----------------|--------|---|----------|

| Carbon (C)      | 1      | - | 1.200 %  |

| Chromium (Cr)   | 16     | - | 18.000 % |

| Iron (Fe)       | 78     | - | 83.100 % |

| Manganese (Mn)  | 0      | - | 1.000 %  |

| Molybdenum (Mo) | 0      | - | 0.800 %  |

| Phosphorus (P)  | 0      | - | 0.040 %  |

| Silicon (Si)    | 0      | - | 1.000 %  |

| Sulfur (S)      | 0      | - | 0.015 %  |

Table 3: Chemical composition of hay, assuming it has the same composition as grass [11], but with less water [12].

| Material          | Amount   |

|-------------------|----------|

| Water (H2O)       | 14.000 % |

| Lignin (C9H10O2)  | 28.667 % |

| Lignin (C10H12O3) | 28.667 % |

| Lignin (C11H14O4) | 28.667 % |

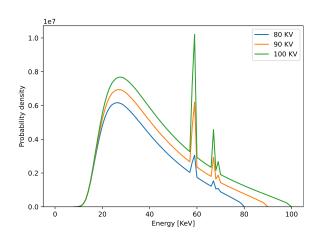

Figure 3: X-ray filtered bremsstrahlung spectrum simulation using Tungsten anode. These are the actual values produced by an X-ray source at different voltages. Similarly, increasing the ampere would increase the curves' magnitude but retain the same relative distribution. Plot is from [14].

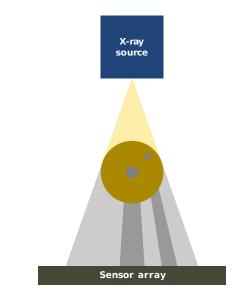

Figure 4: Visualization of the cone effect that arises from having a single point source. The brown circle depicts a potato with two internal objects with a higher density than the potato, resulting in darker shadows.

XCOM NIST database [13], we get the attenuation curves in Figure 2 by entering these compositions. Suppose we choose an energy right where the two curves overlap, then we cannot tell the difference from the penetrated beam since both materials will absorb the same amount of energy. So, to tell the two materials apart, we want to choose an energy level, where the amount of energy absorbed by each of the materials is distinguishable. For example, such a choice could be below  $10^2$  or above  $10^4$  for the needle and hay in Figure 2. While we can now choose energies that produce clear contrasts between two materials, it might not be as easy once we go to three materials. To solve this, we can gather even more information about the scanned materials by capturing the beam produced at two different energies.

An X-ray source produces X-ray photons controlled by two parameters: voltage, the energy of the photons, and ampere, the number of photons. However, these parameters describe the values going into the X-ray source, not the actual energies and amounts produced. Figure 3 shows the simulated energies produced at different voltages. We see that the energies span a wide range rather than a specific one but that the maximum energy reached matches the input voltage. We can handle the low-energy photons by using clever filtering techniques. E.g., suppose we are only interested in photons at energies higher than 30 KeV. In that case, we can insert a filter, which will absorb all the low-energy photons – with high probability. We cannot filter the high energies simultaneously, but we control the maximum energy through the voltage.

When looking at the photons, we must consider that they are all produced from a single source, effectively emitting a light cone. When we have our scanned subject right below this single source, the shadows cast will not be precisely below the subject, resulting in the shadows becoming "stretched" based on the angle. Figure 4 illustrates this effect, where we can see that even though the upper-right object is only half the width of the center object, the relational width, once they hit the detector, is only 1.59, where the actual relation is 2.00. This cone effect could hide some objects; lighter objects could "hide in the shadow" of denser objects. The cone effect also introduces a halo effect on the

Figure 5: Halo effect on an X-ray image with a single X-ray source.

images. Figure 5 shows the effect on a resulting X-ray image, where we see a "glow" irradiating from the center of the image. To produce clean images, we would have to correct this as well.

A final note about X-rays is that the high energies can be destructive, both for living tissue and sensitive machinery. It is generally not a problem for small bursts of exposure for living tissue since the probability of the photons interacting directly with the tissue is relatively low. Inversely, longer exposing times raises the probability of interaction. There is the probability of introducing or draining electrons, currently carrying a state, occurring both in wires or transistors for electronics. As such, any running electronics under X-ray exposure has a probability of producing random errors. In the resulting images, these random errors usually become *salt-and-pepper* noise, which are single pixels attaining either minimum or maximum possible value.

Furthermore, the introduction of electrons can translate into an overload of electrons in the system, resulting in permanent damage to the internal components. The longer exposure time, the higher the probability, which means electronics deteriorate over prolonged exposure. Therefore, we must continuously do calibration and corrections, as the X-ray side-effects would otherwise have too strong an impact.

While all of the effects covered in this chapter do not directly affect the program produced in this thesis, it is essential to keep these details in mind, as they directly limit the program's capabilities. For instance, we can only make predictions as good as the images we receive, so choosing the proper voltage and ampere to maximize contrast for the given materials is essential.

# $I\,M\,A\,G\,I\,N\,G$

Like X-ray, we have to dive into imaging technology, as there are some physical effects that we have to consider, as these directly impact the images. Cameras are devices that capture the light reflected off of a surface as a two-dimensional grid of values. Depending on the surface it hits, the light will be oscillating at different wavelengths. Humans interpret these wavelengths as color, with blue at the low end of the spectrum and red at the high end.

We convert the analog signal into a digital signal through discretization to obtain digital images. The most common sensors are Charge Coupled Device (CCD) or Complementary Metal Oxide Semiconductor (CMOS), which work by having a grid of sensors with each sensor constituting a pixel in the resulting image. As a result, the density of the sensor grid directly controls the image resolution. When a photon hits one of these sensors, the photon is converted into electrons, essentially counting as a photon hit. When capturing an image, the camera exposes the sensors to the scene for a set amount of time, during which the sensor accumulates the number of photons hitting it. The longer the exposure time, the brighter the image since more photons will be counted. After the exposure, the camera drains the accumulated values into a matrix of values, which it stores on its internal storage as the final image, resetting the accumulators along the way. Each color has a sensor array for color images, which commonly constitutes red, green, and blue. Each sensor array filters the photons, only allowing photons of a specific wavelength to pass through, essentially only counting photons of a specific wavelength to pass through, essentially only counting photons of a specific wavelength - or color.

Images consist of multi-dimensional matrices of values. The last dimension of the matrix varies depending on what they are representing, usually relating to the number of channels. For example, the last dimension of black and white images is 1, whereas the last dimension of color images is 3 to 4. Some cameras are focused on one task, while others carry the functionality to do both. The fourth channel is commonly used as an alpha channel, describing the pixel's opacity, which is often used in computer graphics and thus not captured by a camera.

The exposure time relates to the sampling rate, as a reduced exposure time translates to a higher sampling rate. The sampling rate is essential when dealing with moving objects. Consider an object whose reflected photons would hit a single sensor if the object were stationary. Let us assume that the object is moving with a velocity corresponding to moving one pixel along the sensor grid in one direction every millisecond. If the exposure time is five milliseconds, the object will contribute photon counts to five sensors, giving the effect of a stretched, less intensive object in the resulting image. This effect is known as *motion blur* and shows as a stretching and blurring of the moving objects in the direction the object is moving.

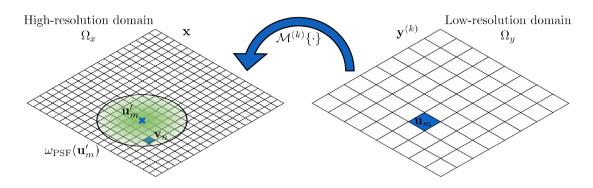

Figure 6: Visualization of how the low-resolution domain relates to the high-resolution domain. Image from [16].

#### 4.1 SUPER RESOLUTION

The master's thesis by Simon Nyrup titled "Applied Super-Resolution for X-Ray Imaging - Virtual Potatoes And How To X-Ray Them" [15] was supervised as part of this Ph.D. thesis and is covered in Appendix B.1.7. The master's thesis had two parts: super-resolution and building an X-ray simulator (covered in Section 5.1).

Half of the thesis looked at whether we could counter motion blur through a series of images of the same object, in turn improving image resolution. It leveraged the fact that an image discretizes the natural world, which means it is a low-resolution observation of a high-resolution domain. This restoration is known as *Super-resolution*. Super-resolution is the reverse operation, where we try to restore an image to the high-resolution domain through the probability that the photon count of a sensor originated from a distribution in the high-resolution domain. Figure 6 visualizes this probability relation between the two domains.

The master's thesis proposes the Iterative Re-Weighted Super-Resolution (IRWSR) algorithm, which is a Multi-Frame Super-Resolution (MFSR) algorithm. To perform super-resolution, we first have to match up the image series. After matching, each image x contributes its values to the resulting high-resolution image  $\hat{x}$  through its weights  $\alpha$ ,  $\beta$ , and  $\lambda$ . The algorithm alters between estimating the image and the weights and runs for multiple iterations.

After a set number of iterations, we obtain the reconstructed high-resolution image  $\hat{x}$ . Figure 7 shows the original high-resolution image, the same image artificially degraded, and the reconstructed high-resolution image based on the artificially degraded image. We see that the stripes on the scarf and some facial features are more defined than the degraded image, showing that the image quality has improved.

#### 4.2 SEAM CARVING

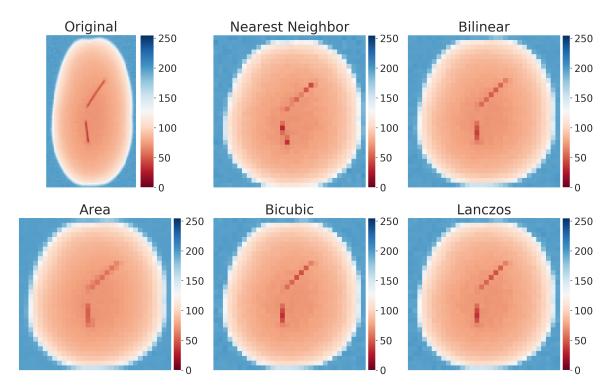

While we want high-resolution images that carry a high degree of information, the higher resolutions increase the computational complexity required to process them. Downscaling the images allows us to retain some of the information but still discards potentially valuable information. The most general approach is interpolation, where neighboring pixels contribute equally to the downscaled

Figure 7: Images showing the process of super-resolution. Left shows the original image. Middle shows the artificially degraded image. Right shows the artificially degraded image upscaled through the IRWSR algorithm. Images from [15]

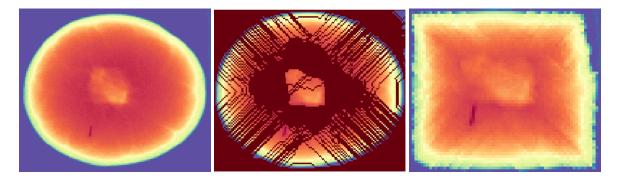

Figure 8: Seam carving applied to an orange with a needle inside. From the left we see the original image, the seams that are removed, and the image with the seams removed. The image has been reduced from 115x135 to 57x67. Images from [14].

image. However, this approach is not viable for small features, as they can get squashed, given that their contribution will have less of an impact due to their size. Optimally, we would remove the uninteresting parts of the image while keeping the prominent parts intact.

The master's thesis by Aleksandar Topic titled "Automating Classification in Food Inspection" was supervised as part of this Ph.D. thesis. Amongst other things, this thesis investigated the content-aware image resizing algorithm known as *seam carving*. The algorithm works iteratively in either the horizontal or vertical directions, where it computes an energy map of the image, describing the change in information. The idea is to find a path through the image in either direction that carries minimal information. The intuition is that we will have made the least intrusive data manipulation concerning contrasting features by removing this path. Suppose we have an image with a large homogeneous region. By removing a path through this region, a homogeneous region will still exist, but all of the other details of the image remain. Figure 8 depicts an image before and after removing seams. Notice how the algorithm preserves the center and the needle while reducing the background and homogeneous regions.

We can express the algorithm as a single equation:

$$M(i,j) = E(i,j) + \min[M(i-1,j-1), M(i-1,j), M(i-1,j+1)]$$

(2)

M is the minimum energy matrix, and E is the energy matrix. The row i of M has its values obtained from the accumulated sum of a path through the previous rows. The energy map, E, can be computed in many different ways, but the straightforward approach uses Sobel filters. In this case, the energy

map consists of the gradients of the input image in the x and y directions. With this algorithm, we can downscale images without removing prominent features.

# X-RAY IMAGING

As the name implies, X-ray imaging applies traditional imaging technologies to light in the X-ray spectrum. However, where regular sensors can capture photons in the visible spectrum, photons in the X-ray spectrum cannot be captured, as a large percentage of these photons will penetrate the sensor. One solution is to "convert" the photons back into the visible spectrum. The most common method used for converting x-rays to photons is a scintillator.

A scintillator is a material that, when hit by photons in the X-ray spectrum, gets excited, in turn emitting photons in the visible spectrum. Different scintillators have different properties, such as the number of photons emitted, the number of X-ray photons penetrating the scintillator, and the required thickness. An essential property of scintillators is how fast they become calm again. This calming factor is especially prominent when scanning moving objects, as light pollution will show a blurring effect, similar to motion blur in traditional imaging but more prominent in X-ray imaging.

X-ray imaging uses either an array of sensors (a *line scanner*) or a grid of sensors (an *area scanner*). There is a scintillator layer between the source and the detector regardless of which technique we utilize. Line scanners have the advantage of running at higher capture rates, given that there are fewer sensors to drain in between each capture. Their disadvantage comes from moving the subject to be scanned to construct a two-dimensional image as they only capture one row. Area scanners have the advantage of not reconstructing the image, as the grid of sensors handles this. Their disadvantage is their lower capture rates, which translates into increased exposure time, resulting in additional motion blur.

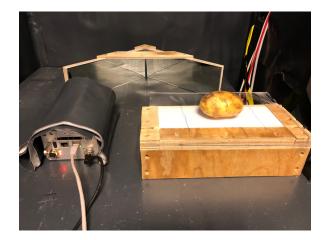

Both types of cameras have the problem of deterioration by prolonged exposure to X-rays. The complexity of electronics determines the rate of failure, or rather the probability of a failure happening - the denser the electronics, the higher probability of an X-ray photon interacting with the matter. As line scanners are less complex than area scanners, they are less likely to fail, increasing their popularity in X-ray imaging. One way of circumventing the deterioration problem is by using mirrors to divert, or *bend*, the visible light while being penetrated by most X-rays. As such, we can bend the visible light into a shielded region where the detector resides by using mirrors, such as Figure 9 depicts. While some X-rays will still directly hits the detectors, there will not be as many, resulting in a lower probability of failure.

Figure 9: Closeup of how the camera is shieled by using mirrors. Image from [15].

#### 5.1 X-RAY IMAGING SIMULATOR

The master's thesis by Simon Nyrup titled "Applied Super-Resolution for X-Ray Imaging – Virtual Potatoes and How to X-Ray Them" [15] was supervised as part of this Ph.D. thesis and is covered in Appendix B.1.7. The master's thesis had two parts: super-resolution (covered in Section 4.1) and building an X-ray simulator.

The motivation behind building the simulator arose during the 2020 covid pandemic. We needed X-ray images, but we could not go to Newtec to use their setup, so we looked into simulating these images. The simulator uses an approximation of X-ray imaging properties in a discrete space. It functions by having a single point in the three-dimensional space, acting as the X-ray source. At the bottom of the space, a grid of points spread across a plane acts as the detector. Intuitively, we place the object to be scanned somewhere between the X-ray source and the detector - simulating a real-world setup. The objects are in voxel form, which allows us to vary the internal resolution of the objects by tuning the voxel density.

When rendering an image, the simulator casts a ray for each point in the detector to the X-ray source. We then check each of these paths for whether they pass through an object. If so, the number of voxel hits and the type of the voxels are stored. Then, according to the material, its corresponding mass attenuation curve, the voltage of the source, ampere of the source, and the exposure time, we compute the final pixel value. Figure 10 visualizes this exact setup. Figure 11 shows the images produced by the simulator.

Given that this simulator was not the focus of the master's thesis, there are some shortcomings. Firstly, having the models in a voxel representation has flaws regarding precision and performance. Originally it was chosen due to its ease of implementation. By having the object in a mesh-based representation, we could increase the precision and performance at the cost of increased implementation complexity. Secondly, the simulation model does not truly capture the odd natural behavior of the photons, such as scattering or beam hardening. By applying the mesh-based representation, we could also move more quickly to using some widespread ray-tracing methods found in modern hardware, further increasing the accuracy and performance of the resulting images. Regardless of these flaws, the resulting simulator is a powerful tool for producing X-ray-like images without the risks or capital losses of building an X-ray imaging machine.

Figure 10: Visualization of the X-ray simulator setup. From the left we have a side view, top view, and line approximation through the voxels. Images from [15].

Figure 11: Output from the X-ray simulator. From the left we have anomalies, a potato, and the same potato with the anomalies "inserted" inside. Images from [15].

Figure 12: Raw X-ray image of a potato showing stripes generated by the setup. Image from [17].

#### 5.2 CORRECTING THE IMAGES

We have all these physical effects from the X-ray source, scanned object, scintillator, and camera, so we are getting far from perfect pictures. While we could use them as-is, many of these effects can be reversed or corrected, given that we know their effects when they occur and to what extent they do occur.

The master's thesis by Troels Ynddal, titled "High Throughput Image Processing in X-ray Imaging," [17] ran in parallel at the beginning of this Ph.D. thesis and is covered in Appendix B.1.1. Part of it focused on improving and optimizing data quality in X-ray imaging. While the X-ray setup did have an option to calibrate the images, the process is proprietary and closed-source, leaving no room for improvement. This calibration became a problem since this calibration was too general at times, resulting in strange artifacts. We can apply extra information about the subjects and energies that the detector did not allow by implementing an open-source solution.

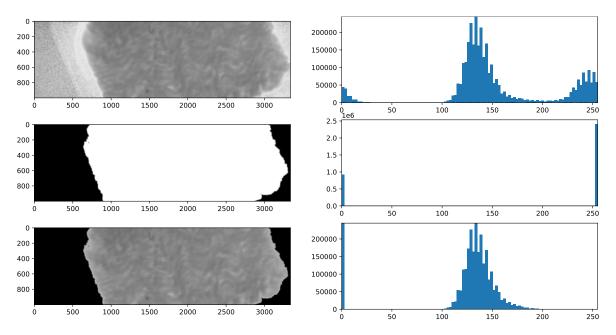

The first step was to correct the raw signal from the detector. As shown in Figure 12, the image contains stripes, known as Fixed-Pattern Noise (FPN). To correct these, we use a Flat-Field Correction (FFC) algorithm. To do this, we need to capture two images for calibration. One, with no X-ray exposure, D, and one with full X-ray exposure, F. Then, for each image, P, we can compensate:

$$N = \frac{P - D}{F - D} \tag{3}$$

As shown in Figure 13, we now have a cleaner image. This process can also counter the halo effect described in Chapter 3. However, as we can see, some noise remains in the image. The master's thesis suggests that using Adaptive Median Filter (AMF) essentially smooths the image, countering the high salt and pepper noise rate commonly found in X-ray imaging. Compared to a regular median filter, AMF allows itself to grow the target region, from which it gains the adaptive part. This adaptiveness is better at removing salt and pepper noise than a regular median filter, as different windows can catch strong outliers.

Finally, the thesis also describes a Region Of Interest (ROI) algorithm for extracting the objects from the rest of the scene and removing the background. The algorithm traverses the image iteratively, marking pixels as belonging to an object based on its previous neighbors. This ROI algorithm benefits line scanners since they create a continuous image, capturing several objects, and because it can work

Figure 13: Corrected X-ray image of a potato from Figure 12. We see that the lines from before are not as intrusive. Image from [17].

Figure 14: The three major steps of the ROI algorithm. From the left we have an image with multiple objects that are found and highlighted with red boxes, one of the potatoes extracted, and the same potato with the background removed. Images from [17].

on one line at a time. Figure 14 shows the steps of the algorithm applied to an image containing several potatoes.

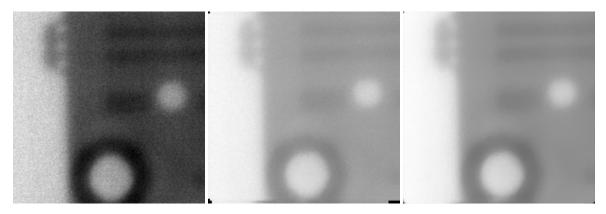

#### 5.3 SUPER-RESOLUTION ON X-RAY IMAGES

As covered in Section 4.1, we have a method for improving the image quality of objects based on a series of images from different angles. We get precisely multiple images of the same object as they move past the sensor for area scanner-based X-ray imaging setups. The idea was then to use super-resolution on this series to obtain a higher-quality image. While we improved the images slightly, as shown in Figure 15, small features did not improve significantly. Furthermore, the computational cost was too high, with the master's thesis author suggesting that using an Machine Learning (ML) approach might produce the same results at a lower computational cost.

Figure 15: Super-resolution applied to X-ray images of a circuit board. From the left we have one of the original low-resolution image, the median of the combined low-resolution images, and the reconstructed super-resolution image. Images from [15].

#### 5.4 EXTREME SEAM CARVING

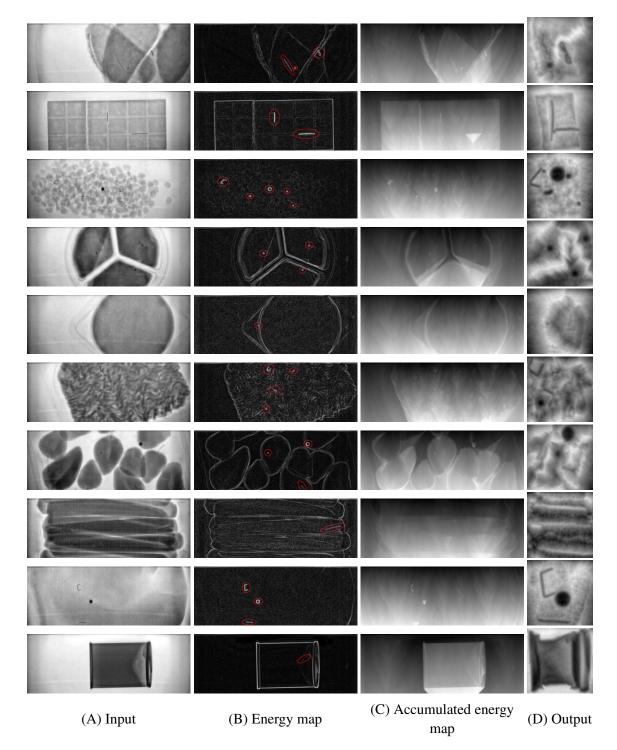

As covered in Section 4.2, we presented seam carving as an image resizing method, which retains prominent features. The results seemed promising, which is why we set up an experiment with multiple X-ray images of different kinds of food. We wanted to see how far we could push the algorithm and whether small foreign objects would remain. This work is covered in our paper, which is under submission.

We gathered the different foods based on whether we thought it would be hard to see anything in the resulting image, which primarily meant whether or not the structure of the foods carried high entropy. Table 4 lists the different foods, the voltage used, and the expected difficulty of seeing the foreign objects. Figure 16 contains the raw X-ray images, their energy map, the positions of the foreign objects, and post seam carving. We see that even though we reduce the size of the images by 98%, we can retain the foreign objects. While we cannot recognize the foods in the seam carved images, we see that the foreign objects are well preserved, both in size and shape. Interestingly, some of the images we thought would be high-difficulty to be some of the best cases. For example, breadcrumbs are almost entirely homogeneous in the X-ray image, having almost perfectly preserved foreign objects in the resulting image. Inversely, the seemingly low-difficulty case of sausages proved poor results, where the metal is hard to find in the seam carved image. This result seems to be due to the air separating the sausages after introducing the foreign object.

The work done in the paper shows that seam carving is a viable method for reducing image resolution while keeping notable features, such as foreign objects.

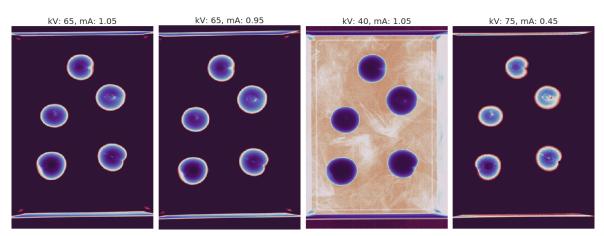

#### 5.5 AUTOMATED TUNING OF THE SETUP

The master's thesis by Aleksandar Topic titled "Automating Classification in Food Inspection" was supervised as part of this Ph.D. thesis and is covered in Appendix B.1.4. Amongst other things, this thesis investigated automatically deriving the optimal parameters for maximizing contrast in an X-ray setup. The method is to take multiple images for mapping the parameter space. Then we compute a histogram for each image, which is then automatically thresholded based on Otsu's method to isolate the objects in the histogram. Finally, we choose the parameters that maximize variance in the

Figure 16: X-ray scans of different foods with varying levels of complexity. We added foreign objects to the foods highlighted in the (B) column with red circles. The input (A) is seam carved to a final size of 72x72 pixels in (D), which translates to 98% of the pixels removed.

| Product            | Voltago usod | Difficulty |

|--------------------|--------------|------------|

|                    | Voltage used | Difficulty |

| Chocolate bars     | 60 kV        | Low        |

| Breadcrumbs (rasp) | 60 kV        | High       |

| Chicken nuggets    | 75 kV        | High       |

| Humus              | 60 kV        | Low        |

| Sausages           | 60 kV        | Low        |

| Strawberries       | 60 kV        | High       |

| Oranges            | 60 kV        | High       |

| Minced meat        | 65 kV        | High       |

| Cold cuts (meat)   | 60 kV        | Low        |

| Coffee beans       | 35 kV        | High       |

| Can of tomato pure | 90 kV        | High       |

Table 4: Overview of the different foods scanned for the seam carving paper. Table is from [18].

Figure 17: X-ray images of plums at a varying voltage and ampere. For the fourth image, we see that the majority of the X-rays penetrate the plums, washing out the edges. For the third image, the voltage is too low to penetrate the plums fully. The first and second images are almost inseparable, but the first image has the largest standard deviation. Image from [14].

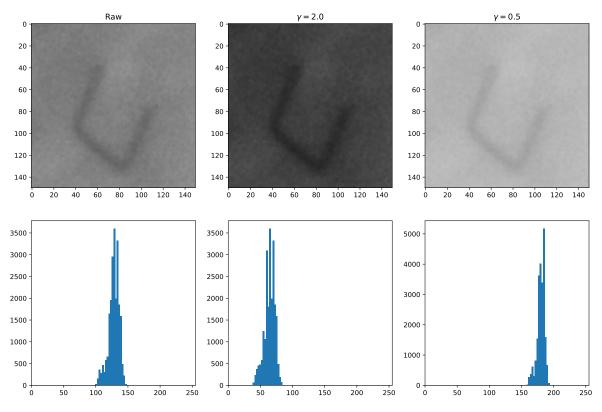

histogram, thus maximizing contrast inside the objects. Figure 17 shows images of plums at varying parameters. We see that we can see the entire plum and its internal structure with the right parameters.

# 6

# SUBCONCLUSION

In this part, we started by covering the fundamental X-ray physics in Chapter 3. While this primarily relates to the work of the other partners of Adaptive Xray InSpection (AXIS), we need to be resilient to the side-effects that X-rays introduce. Then we covered the process of image capturing and how it is a discretized capture of the natural world in Chapter 4. This discretization means that there will be imprecisions and flaws that we have to consider when processing the images. Combining the theory of X-ray physics and image capturing, we present the theory of X-ray imaging in Chapter 5. The key takeaway is that stochastic effects drive X-ray imaging, which we must consider to counter the images' artifacts.

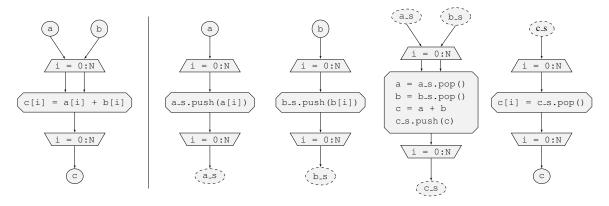

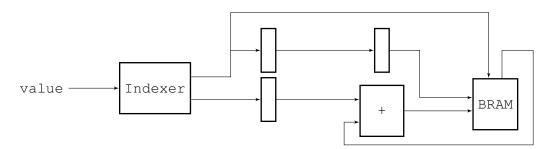

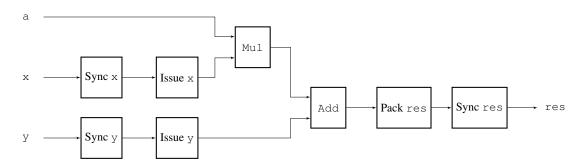

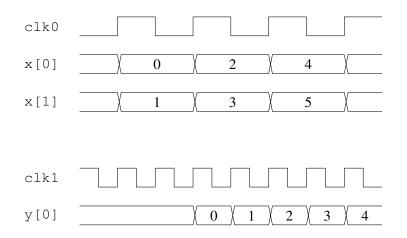

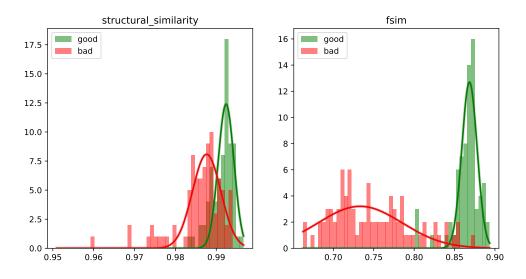

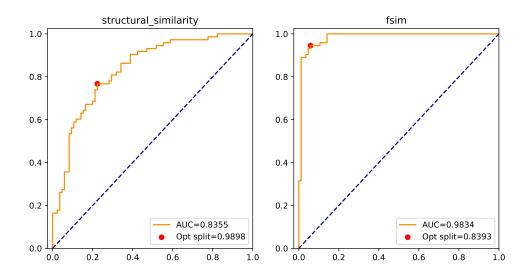

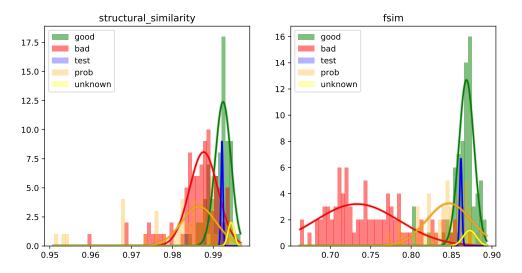

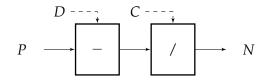

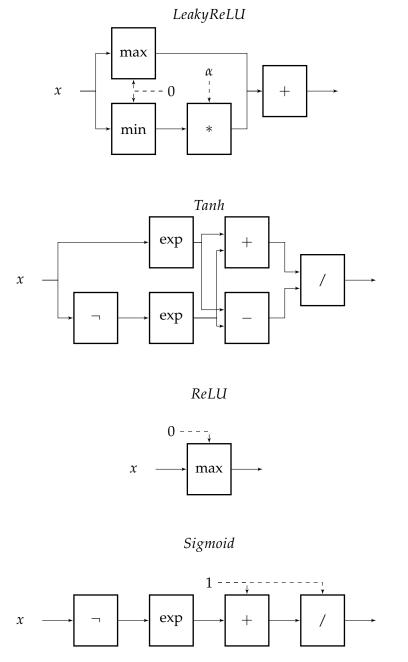

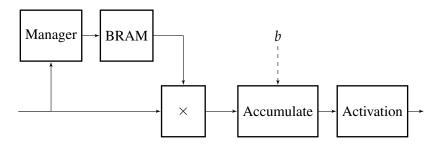

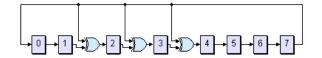

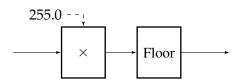

In Section 4.2 we presented the work of a master's student supervised during this Ph.D. thesis: an approach for content-aware image resizing; *seam carving*, a method for removing all of the uninteresting parts of an image. We expanded this work after the student project by applying the method at extreme levels to X-ray images of food, as shown in Section 5.4 and our paper [18]. We removed 98% of the pixels while retaining the foreign objects inserted into the foods. This performance suggests that this method is of strong use for later classification.